Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:45.

- Վերջին փոփոխված 2025-01-23 14:48.

Այս ձեռնարկում մենք պատրաստվում ենք օգտագործել FPGA- ն `արտաքին LED միացումը վերահսկելու համար: Մենք պատրաստվում ենք իրականացնել հետևյալ խնդիրները

(A) Օգտագործեք FPGA Cyclone IV DuePrologic- ի կոճակները `LED- ը վերահսկելու համար:

(B) Պարբերաբար միացրեք և անջատեք լուսադիոդային լուսարձակը

Տեսանյութի ցուցադրում

Լաբորատորիայի ընտրացանկ.

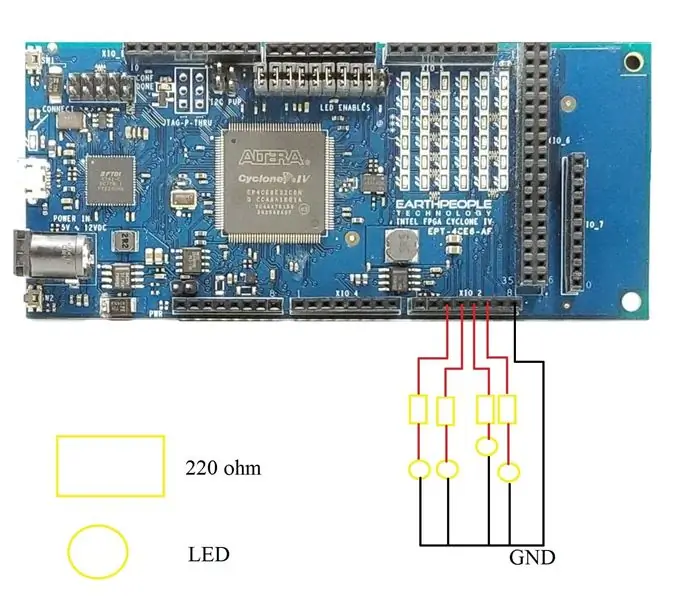

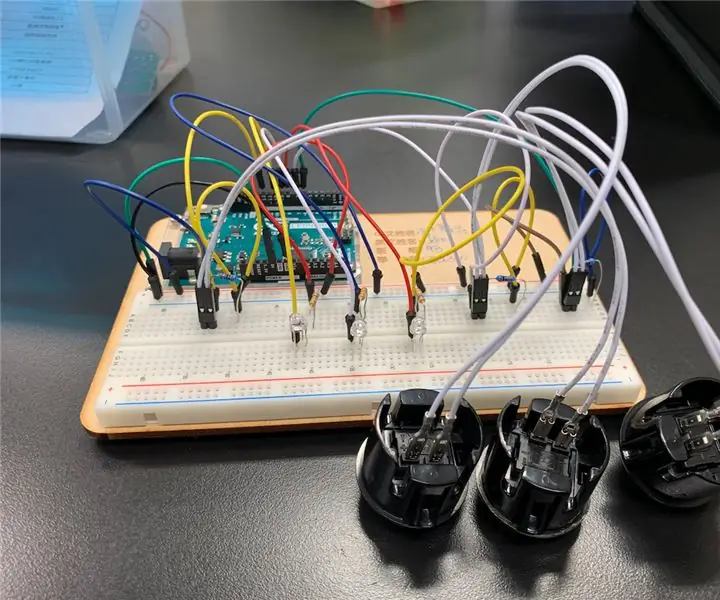

Քայլ 1: Կառուցեք էլեկտրոնային միացում

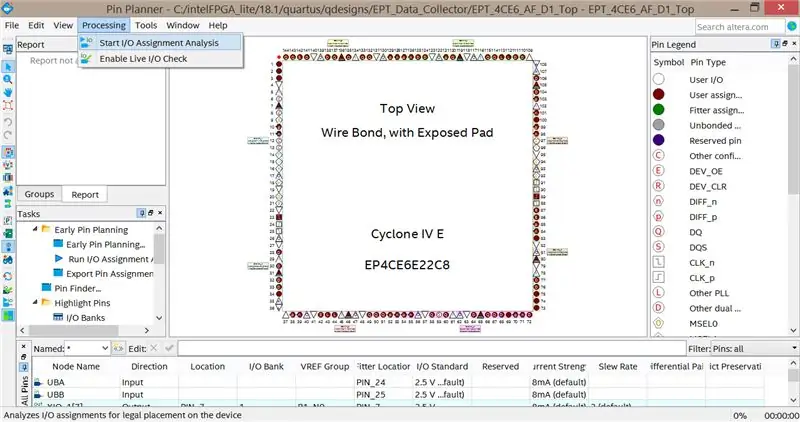

Քայլ 2: Ստուգեք Pin Planner- ը և խմբագրեք Verilog ծածկագիրը

Քայլ 3: Խմբագրել Verilog ծածկագիրը

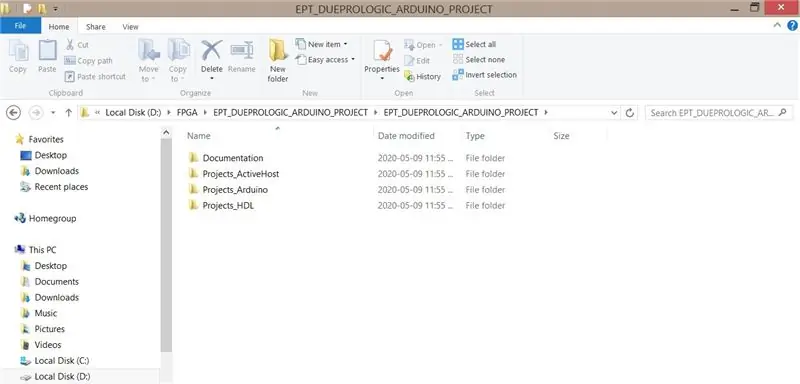

Երբ գնում եք FPGA DueProLogic, դուք պետք է DVD ստանաք: «Projects_HDL» - ը բացելուց հետո դուք պետք է տեսնեք սկզբնական կոդի ֆայլը

Ավելացրեք ընդգծված ծածկագիրը: Այն գրանցում է I/O նավահանգիստները և համարներ նշանակում նավահանգիստներին:

ելքային մետաղալար [7: 0] XIO_1, // XIO-D2-D9

ելքային մետաղալար [5: 0] XIO_2, // XIO-D10-D12

ելքային մետաղալար [5: 0] XIO_3, // XIO-D22-D29

մուտքային մետաղալար [5: 0] XIO_4, // XIO-D30-D37

մուտքային մետաղալար [5: 0] XIO_5, // XIO-D38-D45

ելքային մետաղալար [4: 0] XIO_6_OUT, // XIO-D46-D53

մուտքային մետաղալար [31: 5] XIO_6, // XIO-D46-D53

ելքային մետաղալար [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

մուտքային մետաղալար UBA, // Հրել կոճակի անջատիչներ

մուտքային մետաղալար UBB // Հրել կոճակի անջատիչներ

նշանակել XIO_1 [3] = start_stop_cntrl;

նշանակել XIO_2 [1] = սկիզբ_կապկված; // LED ֆլեշ LED միացված և անջատված

նշանակել XIO_2 [2] = 1'b1; // ելք ԲԱՐՁՐ

նշանակել XIO_2 [3] = ~ UBA; // Հրել կոճակը Ա

նշանակել XIO_2 [4] = UBB; // Հրել B կոճակը

նշանակել c_enable = XIO_5 [2];

նշանակել LEDExt = XIO_5 [5];

Այնուհետեւ մենք պետք է սահմանենք հետաձգման ժամանակաչափ: Մեկնաբանեք ժմչփի սկզբնական կոդը և գրեք ժամաչափի նոր գործառույթ

//-----------------------------------------------

// LED Blinky սկիզբ

//-----------------------------------------------

/*

միշտ @(posedge CLK_66 կամ negedge RST)

սկսել

եթե (! RST)

start_blinky <= 1'b0;

ուրիշ

սկսել

եթե (control_register [7: 4]> 0)

start_blinky <= 1'b1;

ուրիշ

start_blinky <= 1'b0;

վերջ

վերջ

*/

reg [31: 0] նախկին;

սկզբնական սկիզբ

ex <= 32'b0;

start_blinky <= 1'b0;

վերջ

միշտ @(posedge CLK_66)

սկսել

ex <= ex + 1'b1;

եթե (նախկին> 100000000) // բռնկումը միացված/անջատված է ~ 1,6 վայրկյան, ժամացույց 66 ՄՀց

սկսել

start_blinky <=! start_blinky;

ex <= 32'b0;

վերջ

վերջ

//-----------------------------------------------

// LED ուշացման ժմչփ հաշվիչ

//-----------------------------------------------

/*

միշտ @(posedge CLK_66 կամ negedge RST)

սկսել

եթե (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

ուրիշ

սկսել

եթե (նշեք [SELECT_MODE])

led_delay_counter <= ժամանակաչափ_արժեք;

այլ դեպքում (նշեք [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

վերջ

վերջ*/

Քայլ 4: Կազմեք Verilog Code

Սեղմեք «Սկսել կազմումը» Quartus- ում, սխալ հաղորդագրություն չպետք է ստեղծվի:

Եթե դուք ստանում եք սխալի հաղորդագրություն բազմաթիվ կապում: Գնացեք Հանձնարարություններ -> Սարք -> Սարքի և կապի ընտրանքներ -> Երկակի նշանակության կապում -> փոխեք համապատասխան քորոցի արժեքը «Օգտագործեք որպես կանոնավոր մուտք/ելք»:

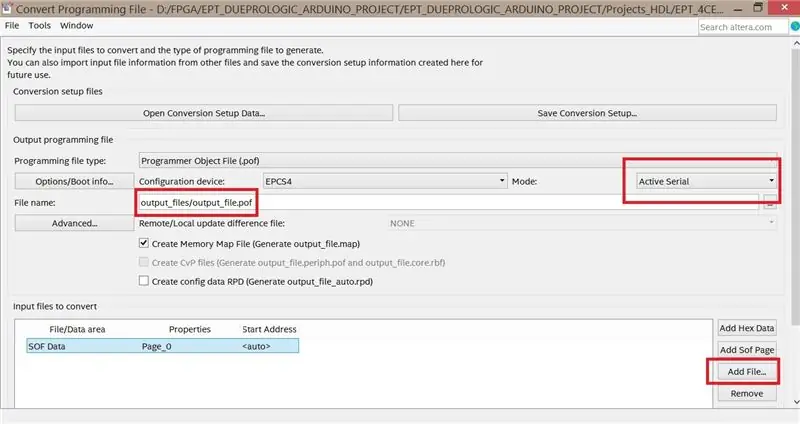

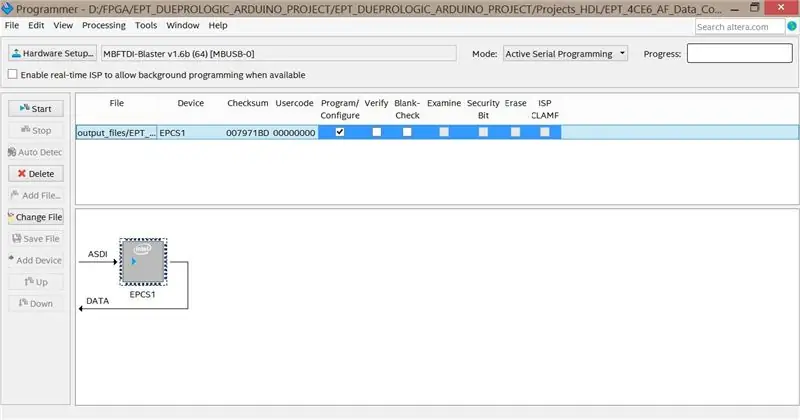

Կազմելուց հետո դուք պետք է անմիջապես ստանաք pof ելքային ֆայլ: Եթե ձեր ծրագրաշարը արդիական չէ, կարող եք ստանալ միայն sof ֆայլ: Երբ դա տեղի ունենա, կտտացրեք «Ֆայլ» Quartus- ում -> «փոխարկել ծրագրավորման ֆայլերը»: Փոխեք կարգավորումները, որոնք նշված են կարմիր տուփերով:

Քայլ 5: Եկեք փորձենք

Ի վերջո, այն պետք է աշխատի !!! Դեղին LED- ը միշտ միացված է: Կարմիր LED- ը թարթում է: Կապույտ LED- ն անջատված է, եթե սեղմում եք B. կոճակը: Կանաչ LED- ն միացված է, եթե սեղմում եք A կոճակը

Խորհուրդ ենք տալիս:

FPGA ցիկլոն IV DueProLogic վերահսկում է ազնվամորի Pi տեսախցիկը `5 քայլ

FPGA Cyclone IV DueProLogic Controls Raspberry Pi Camera. Չնայած FPGA DueProLogic- ը պաշտոնապես նախատեսված է Arduino- ի համար, մենք պատրաստվում ենք փոխանցելի դարձնել FPGA- ն և Raspberry Pi 4B- ն: Այս ձեռնարկում կատարվում են երեք առաջադրանքներ. (A) Միաժամանակ սեղմեք երկու կոճակները FPGA ՝ շրջելու անկյունը

Թարմացրեք VU հաշվիչի լուսարձակը դեպի կապույտ լուսադիոդ ՝ օգտագործելով հին CFL լամպի մասերը. 3 քայլ

Թարմացրեք VU հաշվիչի լուսարձակը դեպի կապույտ լուսադիոդ ՝ օգտագործելով հին CFL լամպերի մասերը. Հին Sony TC630 պտտվող-պտտվող մագնիտոֆոն վերանորոգելիս նկատեցի, որ VU հաշվիչի հետևի լույսի ապակու լամպերից մեկը կոտրված է: աշխատել է, քանի որ կապարը կոտրվել էր ապակու մակերևույթից ներքև: Միակ փոխարինողը, որին կարող եմ ծանոթանալ

FPGA ցիկլոն IV DueProLogic Controls Servo Motor: 4 քայլ

FPGA Cyclone IV DueProLogic Controls Servo Motor: Այս ձեռնարկում մենք պատրաստվում ենք գրել Verilog ծածկագիրը `սերվո շարժիչը վերահսկելու համար: Servo SG-90- ը արտադրվում է Waveshare- ի կողմից: Երբ դուք գնում եք servo շարժիչ, կարող եք ստանալ տվյալների թերթիկ, որը ցույց է տալիս աշխատանքային լարումը, առավելագույն ոլորող մոմենտը և առաջարկվող Pu

Ulsարկերակային լուսադիոդ ՝ օգտագործելով 555 ժամաչափ և պոտենցիոմետրեր ՝ 4 քայլ

Ulsարկերակային լուսադիոդ ՝ օգտագործելով 555 ժամաչափ և պոտենցիոմետրեր. Ողջույն: Այս ուսանելի ծրագրում մենք ձեզ ցույց կտանք, թե ինչպես կարելի է կառուցել LED Dimmer միացում, որն աշխատում է կարգավորելի ժամանակացույցի օղակով `օգտագործելով պոտենցիոմետր, 555 ժամաչափ և միացման հիմնական այլ բաղադրիչներ: Այս նախագծի գաղափարը մենք սկզբում ստացանք

Լուսացույցի լուսադիոդ ՝ 4 քայլ

Լուսացույցի լուսադիոդ. Inatedագումը ՝ https://www.makeuseof.com/tag/arduino-traffic-ligh..The Arduino լուսացույցը արագ, հեշտ և զվարճալի նախագիծ է, որը կարելի է անել մեկ ժամից պակաս: Կատարված փոփոխություններ