Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:48.

- Վերջին փոփոխված 2025-01-23 14:48.

UART- ը նշանակում է ունիվերսալ ասինխրոն ընդունիչ հաղորդիչ: Այն սերիական հաղորդակցության ամենահայտնի և ամենապարզ արձանագրությունն է: Այս ուսանելի ծրագրում դուք կսովորեք, թե ինչպես նախագծել UART մոդուլ VHDL- ում:

Քայլ 1. Ի՞նչ է UART- ը:

Տարբեր ծայրամասային սարքերի հետ հաղորդակցվելու համար պրոցեսորները կամ վերահսկիչները սովորաբար օգտագործում են UART հաղորդակցություն: Դա պարզ և արագ սերիական հաղորդակցություն է: Քանի որ UART- ը նվազագույն պահանջ է գրեթե բոլոր պրոցեսորներում, դրանք սովորաբար նախագծվում են որպես Soft IP միջուկներ VHDL- ում կամ Verilog- ում `կրկին օգտագործելիության և ինտեգրման հեշտության համար:

Քայլ 2: Տեխնիկական պայմաններ

Նախագծված UART- ի բնութագրերը տրված են ստորև.

* Ստանդարտ UART ազդանշաններ:

* Կարգավորելի բաուդ փոխարժեքը 600-115200-ից:

* Նմուշառում = 8x @receiver

* FPGA ապացուցված դիզայն ՝ Xilinx Artix 7 տախտակի վրա:

* Փորձարկվել է UART- ի ծայրամասային սարքերի վրա, Hyperterminal- ը հաջողությամբ `բոլոր բաուդրատները

Քայլ 3: Դիզայնի մոտեցում

-

Մենք նախագծելու ենք 3 մոդուլ, որոնք հետագայում ինտեգրվելու ենք UART- ը ավարտին հասցնելու համար:

- Հաղորդիչի մոդուլ. Հոգ է տանում սերիական տվյալների փոխանցման մասին

- Ստացողի մոդուլ. Հոգ է տանում սերիական տվյալների ընդունման մասին

- Baud գեներատոր Մոդուլ. Հոգ է տանում Baud ժամացույցի ստեղծման մասին:

- Baud գեներատորի մոդուլը դինամիկ կարգավորելի է: Այն ստեղծում է երկու բաուդ ժամացույց հիմնական ժամացույցից `ըստ ցանկալի արագության: Մեկը ՝ հաղորդիչի, մյուսը ՝ ստացողի համար:

- Ստացողի մոդուլը օգտագործում է ընտրանքի արագությունը 8x ՝ նվազագույնի հասցնելու ընդունման սխալի հավանականությունը, այսինքն ՝ ընդունիչի բաուդ ժամացույցը 8x հաղորդիչ բաուդ ժամացույց է:

- Հսկիչ ազդանշաններ `փոխանցումը և ընդունումը վերահսկելու համար, ինչպես նաև ընդհատման ազդանշանը:

- Ստանդարտ UART սերիական ինտերֆեյս ՝ առանց պարիտետային բիտի, մեկ կանգառի և մեկնարկի բիթ, 8 տվյալների բիթ:

- Hostուգահեռ ինտերֆեյս հաղորդավարի, այսինքն ՝ պրոցեսորի կամ վերահսկիչի հետ հաղորդակցվելու համար, որը կերակրում և ստանում է զուգահեռ տվյալներ դեպի և UART- ից:

Քայլ 4: Սիմուլյացիայի արդյունքներ

Քայլ 5: Կից ֆայլեր

* UART հաղորդիչ մոդուլ -vhd ֆայլ

* UART ստացողի մոդուլ - vhd ֆայլ

* Baud գեներատորի մոդուլ - vhd ֆայլ

* UART մոդուլ - Վերևի մոդուլները ինտեգրող հիմնական վերին մոդուլը `vhd ֆայլ

* UART IP Core- ի ամբողջական փաստաթղթերը `pdf

Eriesանկացած հարցի համար ազատ զգալ կապվեք ինձ հետ ՝

Միտու Ռաջ

հետևեք ինձ.

Հարցերի համար դիմեք ՝ iammituraj@gmail.com

Խորհուրդ ենք տալիս:

LoRa- ի վրա հիմնված գյուղատնտեսության տեսողական մոնիթորինգի համակարգ Iot - Նախագծված դիմումի ձևավորում Firebase- ի և անկյունայինի միջոցով. 10 քայլ

LoRa- ի վրա հիմնված գյուղատնտեսության տեսողական մոնիտորինգի համակարգ Iot | Firebase & Angular- ի միջոցով ճակատային հավելվածի նախագծում. Նախորդ գլխում մենք խոսում ենք այն մասին, թե ինչպես են սենսորները աշխատում loRa մոդուլով ՝ հրակայունի Realtime տվյալների բազան համալրելու համար, և մենք տեսանք շատ բարձր մակարդակի դիագրամ, թե ինչպես է աշխատում մեր ամբողջ նախագիծը: Այս գլխում մենք կխոսենք այն մասին, թե ինչպես կարող ենք

Հիմնական պարամետրերի ավտոմատ վերահսկմամբ ակվարիումի ձևավորում. 4 քայլ (նկարներով)

Ակվարիումի դիզայն հիմնական պարամետրերի ավտոմատացված վերահսկմամբ. Ներածություն Այսօր ծովային ակվարիումի խնամքը հասանելի է յուրաքանչյուր ակվարիումի համար: Ակվարիում ձեռք բերելու խնդիրը դժվար չէ: Բայց բնակիչների լիարժեք կենսապահովման, տեխնիկական խափանումներից պաշտպանվելու, հեշտ և արագ սպասարկում և խնամք

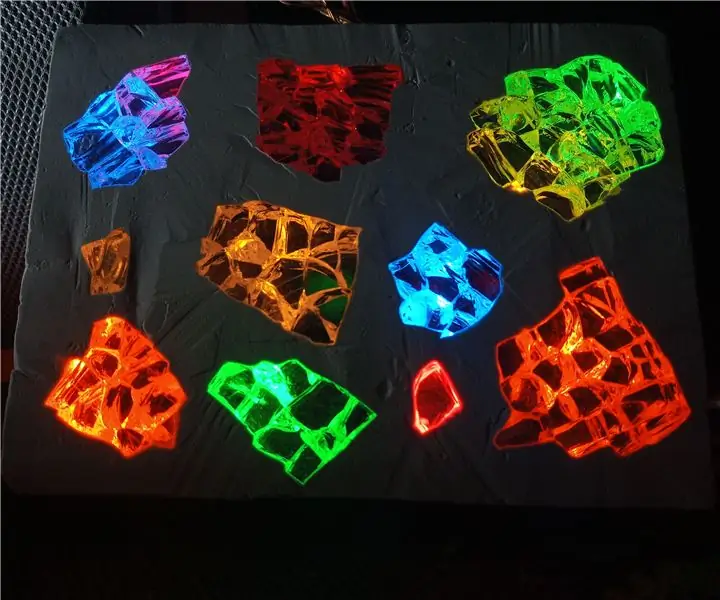

Գունավոր LED ձևավորում. 9 քայլ (նկարներով)

Collorfull LED Decoration

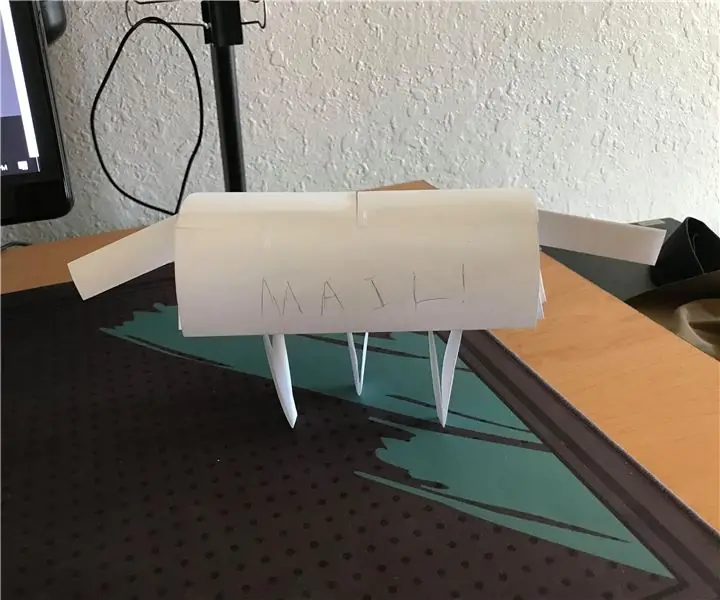

Փոստի բոտ UX ձևավորում. 6 քայլ

Mail Bot UX դիզայն. Սա ռոբոտ է, որը գոռում է ձեզ վրա, երբ փոստ ունեք: Ձեզ անհրաժեշտ է սոսինձ և ժապավեն

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. 5 քայլ

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. Այս ուսանելի ծրագրում մենք պատրաստվում ենք նախագծել պարզ VGA վերահսկիչ RTL- ում: VGA Controller- ը թվային միացում է, որը նախատեսված է VGA էկրաններ վարելու համար: Այն կարդում է Frame Buffer- ից (VGA Memory), որը ներկայացնում է ցուցադրվող շրջանակը և առաջացնում անհրաժեշտություն