Բովանդակություն:

- Հեղինակ John Day [email protected].

- Public 2024-01-30 09:45.

- Վերջին փոփոխված 2025-01-23 14:48.

JDM- ը հանրաճանաչ PIC ծրագրավորող է, քանի որ այն օգտագործում է սերիական նավահանգիստ, բաղադրիչների նվազագույն քանակ և չի պահանջում սնուցման աղբյուր: Բայց այնտեղ խառնաշփոթ կա, ցանցում ծրագրավորողների բազմաթիվ տատանումներով, որոնք են PIC- ով աշխատում: Այս «ուսանելի» հոդվածում մենք փորձարկում ենք JDM- ը, և ես ցույց եմ տալիս, թե ինչպես կարելի է նմանակել Spice- ը, որը կպատասխանի ձեր բոլոր հարցերին:

Պարագաներ

LTspice, որը կարելի է ներբեռնել անալոգային սարքերից այստեղ:

Ձեզ նույնպես պետք են JDM սխեմայի ֆայլերը այստեղ:

Քայլ 1: Սերիայի նավահանգստի պահանջները

JDM- ն պահանջում է սերիական նավահանգիստ, որը համապատասխանում է EIA232 բնութագրին, իդեալականորեն ` +12/-12 Լարման մակարդակներով:

Համաձայն Texas Instruments Line Driver MC1488 տվյալների թերթիկի (Նկար 3)

Ելքային դիմադրություն = 4 Վ/8 մԱ = 500 օմ:

Կարճ միացման հոսանքի սահմանաչափը = 12 մՎ, առանց որևէ սահմանափակման `չիպի վնաս:

Առաջարկվում է գծի ընդունիչի մուտքային դիմադրություն = 3k- ից մինչև 7k ohm:

Հին աշխատասեղան համակարգիչների սերիական նավահանգիստներն օգտագործում են +12v/-12V այս պահանջը բավարարող:

Ավելի նոր համակարգիչների վրա սերիական նավահանգիստներն օգտագործում են ավելի ցածր լարման: JDM- ը կարող է աշխատել կամ չաշխատել. Պատասխանը ավելի բարդ է:

Քայլ 2: PIC ծրագրավորման պահանջներ

PIC ծրագրավորման պահանջներին վերաբերող տեղեկատվությունը ստացվում է Microchip- ից: Վերոնշյալը բնորոշ սարքի համար է:

Քայլ 3: JDM- ի ճշգրտում

Արդյո՞ք JDM- ի սկզբնական կայքը կորել է ժամանակի մառախուղի մեջ: Սա մեզ թույլ է տալիս կռահել, թե ինչ էր ի սկզբանե դիզայները նախատեսում ճշգրտման համար:

- Տրամադրեք VDD = 5V, և առավելագույնը IDD = 2mA («վարդակից» տարբերակի համար)

- Տրամադրեք VHH = 13V, իսկ մինչև IHH = 0.2mA առավելագույն:

- MCLR Բարձրացման ժամանակը tVHHR = 1uS առավելագույնը

- ICSP- ի տարբերակը պետք է կարողանա MCLR- ն իջեցնել թիրախի 22k քաշման դիմաց:

Քայլ 4: Շրջանի նկարագրություն

Նկար JDM1- ը հիմնված է «ստանդարտ» JDM սխեմայի վրա, որը վերցված է PICPgm վեբ կայքից: Սա «PIC in Socket» ծրագրավորողն է, որտեղ PIC- ը ուժ է վերցնում TX և RTS կապերից: Սկզբնական դիագրամը դժվար էր հասկանալ, ուստի ես այն վերագծել եմ ՝ օգտագործելով վերևից ներքև ընթացիկ հոսքի սովորական պայմանականությունը: Եվ ես ավելացրել եմ LED ցուցանիշներ «RESET», «PROG» և «RTS», որոնք անհրաժեշտ են շինարարության և փորձարկման ընթացքում: Հուսանք, որ դրանք որևէ վնասակար ազդեցություն չեն ունենա վարքի վրա:

Շղթայի նախագծման սովորական պայմանը բոլոր հիմքերն է, սակայն JDM- ի հիմնական առանձնահատկությունն այն է, որ սերիական նավահանգիստը (GND) միացված է VDD- ին: Սա խառնաշփոթ է ստեղծում, քանի որ սերիական պորտի ազդանշանները չափվում են GND- ի, PIC ազդանշանների նկատմամբ `տրամաբանական հիմքի (VSS) նկատմամբ:

Երբ TX- ը բարձրանում է, Q1- ն իրեն պահում է որպես երկու կողմնակալ դիոդ: (Q1 կոլեկտորը հակառակ կողմնակալ չէ, ինչպես սովորական տրանզիստորների դեպքում): Q1 կոլեկտորը գանձում է C2- ը, որը սեղմված է VDD+8V- ի վրա Zener- ի կողմից (D3): Q1 թողարկողը 13V է փոխանցում MCLR ծրագրին/ստուգման ռեժիմին:

Երբ TX- ն իջեցնում է այն, C3 կոնդենսատորը լիցքավորվում է D1- ով, իսկ VSS- ը սեղմվում է VDD-5V- ի վրա zener- ով (D5): Նաև TX- ը սեղմված է (VSS-0.6) D1- ով: Q1- ն անջատված է, C1- ն պահպանում է իր գանձումը ծրագրավորման հաջորդ զարկերակի համար: MCLR- ը սեղմված է 0V- ով D2- ով, այնպես որ PIC- ն այժմ վերակայված է:

Երբ RTS- ը բարձր է, ժամացույցը փոխանցվում է PGC- ին: D4 սեղմիչ PGC բարձր VDD տրամաբանությամբ: Երբ RTS- ը ցածր է, C3 կոնդենսատորը լիցքավորվում է D6- ով, իսկ VSS- ը սեղմվում է VDD-5V- ի վրա zener- ով (D5): D6 սեղմում է PGC- ն VSS- ում կամ տրամաբանական 0 -ում:

Programրագրավորման ընթացքում DTR- ով ուղարկվող տվյալները կարդացվում են PGD- ով, որը PIC- ը կարգավորում է որպես մուտքագրում: Երբ DTR- ը բարձր է, Q2- ը հանդես է գալիս որպես «արտանետողների հետևորդ», իսկ PGD- ի լարումը մոտ (VDD-0.6) կամ տրամաբանություն 1. Երբ DTR- ը ցածր է, Q2- ը հանդես է գալիս որպես վատ տրանզիստոր (արտանետողի և կոլեկտորի քորոցները հակադարձվում են): Q2- ը ցածր է PGD- ն, որը սեղմված է D7- ով VSS- ում կամ տրամաբանական 0 -ում:

Ստուգման ընթացքում PIC- ը կարգավորում է PGD- ն որպես ելք ՝ տվյալների սերիական նավահանգիստ ուղարկելու համար: DTR- ը պետք է սահմանվի բարձր, իսկ տվյալները կարդում են CTS- ով: Երբ PGD- ի ելքը բարձր է, Q2- ն անջատված է, CTS = DTR = +12V: Երբ PGD- ի արտադրանքը ցածր է, Q2- ը միացված է: Q2 կոլեկտորը DTR- ից հոսանք է քաշում (12V+5V)/(1k+1k5) = 7mA և ցածր CTS- ը քաշում դեպի VSS:

Քայլ 5: Պատրաստվեք մոդելավորման համար

Ներբեռնեք LT համեմունք, պահեք և բացեք այստեղ տրամադրված սխեմայի ֆայլերը (*.asc): Շղթան նմանակելու համար մենք պետք է որոշ մուտքեր տանք դրան, այնուհետև «հետևենք» ելքերին: V1, V2 V3 մոդելավորում են 12V սերիայի պորտը ելքային դիմադրությամբ R11, R12, R13:

- V1- ն առաջացնում է 2 Pրագրային իմպուլս TX- ի վրա `0.5ms- ից 4.5ms

- V2- ը տվյալների զարկերակների առաջացում է առաջացնում DTR- ի վրա ՝ 1.5 -ից մինչև 4.5ms

- V3- ը RTS- ում առաջացնում է ժամացույցի իմպուլսներ 0.5 -ից 3.5msms

V4, X1, R15 և R16 բաղադրիչները սիմուլյացիայի մի մասն են:

- V4- ը տվյալների ստուգման համար առաջացնում է 2 իմպուլս 2.5 -ից 4.5ms- ի դեպքում:

- Jumper X1- ը մոդելավորում է PGD- ի OUTPUT- ը:

- R15, R16- ը նմանեցնում է PIC- ի «բեռնումը» VDD- ի և MCLR- ի վրա:

Քայլ 6. ICSP- ի փոփոխություններ

Նկար JDM3- ը ցույց է տալիս «միացված» ծրագրավորման տարբերակը: Սկզբնաղբյուրի փոփոխություններն են

- ZIF վարդակը փոխարինեք ICSP միակցիչով:

- PIC- ն այժմ սնուցվում է թիրախային սխեմայի մատակարարման միջոցով (V5):

- Հեռացրեք 5V զեներ (D5):

- Փոքրիկ 100pF կոնդենսատորը (C4) տեղափոխվում է թիրախային սխեմայի PIC- ի կողքին:

- Հնարավորության դեպքում LED- ները սնուցում են տպատախտակից:

- MCLR ձգվող դիմադրությունը (R10) և դիոդը (D10) պահանջվում են թիրախային սխեմայի վրա:

- ԳՈՇԱՈՄ. Թիրախային տախտակը պետք է ունենա «լողացող» մատակարարում, իդեալականորեն մարտկոց:

- Մի միացրեք նպատակային գրունտը (VSS) համակարգչին/ԱՀ -ին `JDM- ի հետ միաժամանակ միացնելով այլ համակարգչային պորտեր:

JDM1- ի մոդելավորումից հետո C2- ում երկար լիցքավորման ժամանակի խնդիրը ակնհայտ դարձավ: Այնուհետև Fruttenboel- ը կարդալուց հետո պարզվում է, որ C2 և Q1 ավելացվել են որպես բնագրի փոփոխություն: Չեմ կարող մտածել, թե ինչ են նախատեսում անել C2- ն ու Q1- ը ՝ խնդիրներ ստեղծելուց զատ: Այսպիսով, JDM4- ի համար մենք վերադառնում ենք Fruttenboel- ի հին ձևին, որը պարզ և պարզ է հասկանալ: D1 և D3/LED2 սեղմիչ MCLR VSS- ի և VDD+8V- ի միջև: R1- ի արժեքը նվազեցվում է մինչև 3k3, բավական է լուսավորել LED2- ը 12V- ով:

JDM4- ը նաև նախատեսված է ավելի թույլ սերիական նավահանգիստների հետ աշխատելու համար: Երբ TX- ը բարձրանում է բարձր (+9V), TX ընթացիկ աղբյուրը = (9-8)/(1k +3k3) = 0.2 մա, բավական է MCLR- ը բարձր քաշելու համար, չնայած անբավարար LED2 լուսավորելու համար: Երբ TX- ն իջնում է (մոտ -7 Վ), TX ընթացիկ լվացարանը = (9-7)/1k = 2mA: LED1 հոսանք = (7-2 led- ի համար)/(2k7) = 1.8mA: MCLR քաշեք ներքև ընթացիկ = 7-5.5/3k3 = 0.5mA:

Այս սխեման նույնպես փորձարկվել է (JDM5 մոդելավորում) `տեսնելու, թե ինչ է տեղի ունենում սերիական նավահանգիստների հետ +/- 7V նվազագույնի դեպքում, որտեղ անբավարար լարվածություն կա VHH = 13V պահպանելու համար: C1- ի նպատակն այժմ ակնհայտ է դառնում. Բայց հեռացրեք jumper X2- ը (անջատեք LED1- ը), քանի որ MCLR- ը ցածր քաշելու և LED1- ը միասին լուսավորելու համար բավարար հոսանք չկա: Երբ TX- ն իջնում է, TX ընթացիկ լվացարանը = (7V-5.5V)/(1k+3k3) = 0.3mA, պարզապես բավարար է MCLR- ը ցածր քաշելու համար R10- ի դիմաց:

Քայլ 7: Սիմուլյացիայի արդյունքներ

Գրաֆիկական ֆայլերը դիտելու համար ավելի լավ է աջ սեղմել ներքևի հղումների վրա, ապա ընտրել «Բացել հղումը նոր ներդիրում»

Մոդելավորում 1. MCLR- ի, VSS- ի և RTS- ի հետք օրիգինալ JDM1- ի համար: Անմիջապես ակնհայտ են 1, 2 և 3 դիտարկումները:

Սիմուլյացիա 2. MCLR- ի և VSS- ի հետքեր և RTS- ի փոփոխված JDM2- ի համար, որը շտկում է նախկին խնդիրները:

Մոդելավորում 3. JDM2- ի համար տվյալների փոխանցման PGD, VSS և PGC հետքեր `ծրագրի ռեժիմում: 4 դիտում 3,5 mS- ում:

Սիմուլյացիա 4. JDM2- ի համար PGD- ի, VSS- ի և CTS- ի հետք ստուգման ռեժիմում (տեղադրված է թռիչք X1): լավ

Մոդելավորում 5. MCLR, VSS, PGD և PGC հետք JDM3- ի համար: ICSP- ն էլեկտրական հոսանքից օգտվելով լուծում է բազմաթիվ խնդիրներ:

Մոդելավորում 6. MCLR, VSS, PGD և PGC հետք JDM4- ի համար +/- 9V սերիական պորտով: MCLR- ն անմիջապես բարձրանում է, ամբողջովին աշխատում է:

Մոդելավորում 7. MCLR- ի, VSS- ի և TX- ի հետք JDM5- ի համար `+/- 7V սերիական պորտով և X2 թռիչքից հեռացված: C1- ը ստեղծում է +ve խթանում (բարձրացում) MCLR- ի բարձրացող ծայրին, գրեթե բավարար է MCLR- ը TX- ից մինչև 13V բարձրացնելու համար:

Քայլ 8: Եզրակացություններ

Spice- ն իսկապես լավ է բացահայտում շրջանի աշխատանքի «թաքնված գաղտնիքները»: Ակնհայտ է, որ JDM- ի սխեման աշխատում է և համատեղելի է բազմաթիվ PIC չիպերի հետ, սակայն հետևյալ դիտարկումները բացահայտում են հնարավոր սահմանափակումները/համատեղելիության խնդիրները/սխալները:

- MCLR- ի երկար աճի ժամանակը, մինչդեռ C2- ը գանձում է VPP- ին TX- ի առաջին զարկերակի վրա: Չհաջողվեց հստակեցնել 3.

- Սերիական նավահանգիստը գանձում է C2- ը, երբ TX- ը բարձրանում է, իսկ RTS- ը ՝ ցածր: Բայց RTS- ն ունի նաև C3- ի լիցքավորման աշխատանք: Երբ երկուսն էլ տեղի են ունենում միևնույն ժամանակ, դա ավելի մեծ բեռ է ստեղծում RTS- ի վրա, հետևաբար C3- ը սիմուլյացիայի ժամանակ կորցնում է լիցքը (VSS- ը բարձրանում է) 2ms- ում: Չհաջողվեց հստակեցնել 1.

- C3- ն կորցնում է լիցքը (VSS- ն սկսում է բարձրանալ) ժամացույցի զարկերակների դադարեցումից հետո 3.5ms- ում:

- Ո՞րն է C2- ի նպատակը, այն ընդհանրապես անհրաժեշտ է:

Լուծումներ

- Ենթադրաբար, PICPgm- ն օգտագործում է ծրագրային ապահովման «աշխատափուլ»: Այն պետք է կիրառի երկար TX զարկերակ ՝ C2- ին լիցքավորելու համար, այնուհետև ծրագրավորման ռեժիմի՞ց մտնել միայն երկրորդ TX զարկերակից հետո: Սիմուլյացիայի համար ես C2- ի արժեքը իջեցրել եմ 1uF- ի և տալիս 1ms բարձրացման ժամանակ: Իդեալական լուծում չէ:

- Պառակտեք C2 և C3, այնպես որ դրանք ինքնուրույն լիցքավորվում են: JDM2- ի մեկ փոքր փոփոխություն, C2- ը հղվում է GND- ին `VSS- ի փոխարեն:

- Լուծված է JDM3- ով: ICSP- ն շատ ավելի հուսալի է, քանի որ PIC- ը սնուցվում է թիրախային միացումից:

- JDM4- ը լուծում է խնդիրը 1. Սա ուղղակի դիզայն է, որը ընդհանրապես վերացնում է C2- ը:

Քայլ 9: Եվ վերջապես

Պուդինգի ապացույցը ուտելու մեջ է: Այս JDM- ն աշխատում է, այնպես որ շարունակեք օգտագործել այն:

Եվ իմ առաջարկություններն են.

- օգտագործել JDM2- ը վարդակների ծրագրավորման և 12 Վ սերիական նավահանգիստների համար,

- օգտագործել JDM4 ICSP ծրագրավորողի և +/- 9V- ից բարձր սերիական նավահանգիստների համար,

- օգտագործեք JDM4 ՝ jumper X2- ով հեռացված +/- 7V- ից բարձր սերիական նավահանգիստների համար:

Հղումներ:

Անալոգային սարքեր LT համեմունք

picpgm

Fruttenboel

Հետևեք PIC- ի այլ նախագծերի խորամանկ անկյունում

Խորհուրդ ենք տալիս:

Elegoo Super Started Kit Uno R3 ակնարկ. 4 քայլ

Elegoo Super Started Kit Uno R3 ակնարկ. Մի քանի օր առաջ Elegoo- ն ուղարկեց ինձ այս Super Starter Kit- ը փորձարկման համար: Այսպիսով, եկեք տեսնենք, թե ինչ կա ներսում: Այս կոմպակտ պատյանը բացելիս մենք կարող ենք շատ բաներ տեսնել: Շապիկի վրա կա ինդեքս `բոլոր բաղադրիչներով: Ներսում մենք ունենք շնորհակալական քարտ ՝ բոլոր

KS-Garden: ակնարկ. 9 քայլ

KS-Garden: Ակնարկ. KS-Garden- ը կարող է օգտագործվել ոռոգման/օդափոխման համար: համակարգի տուփ - ռելեներ և սնուցման տուփ

Միկրոկառավարիչների ծրագրավորում USBasp ծրագրավորողի հետ Atmel Studio- ում. 7 քայլ

Միկրոկառավարիչների ծրագրավորում Atmel Studio- ում USBasp ծրագրավորողի հետ. Շատ հետազոտություններ կատարելուց և կարդալուց հետո

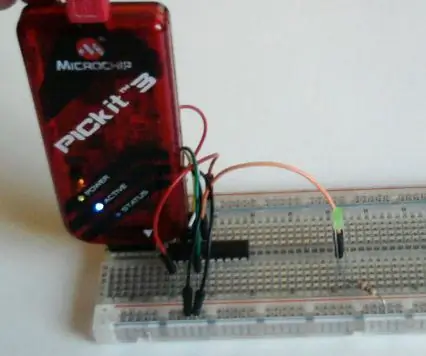

Ինչպես ծրագրավորել PIC MCU- ն PICkit ծրագրավորողի հետ `Breadboard- ի միջոցով. 3 քայլ

Ինչպես ծրագրավորել PIC MCU- ն PICkit ծրագրավորողի հետ `Breadboard- ի միջոցով. PIC (կամ որևէ այլ) միկրոկոնտրոլերների հետ խաղալու համար ձեզ հարկավոր չեն թանկարժեք և բարդ գործիքներ: Այն, ինչ ձեզ հարկավոր է, մի տախտակ է, որտեղ դուք ստուգում եք ձեր սխեման և ծրագրավորումը: Իհարկե, անհրաժեշտ է ինչ -որ ծրագրավորող և IDE: Այս հրահանգում

Նկար 16F676 ICSP ծրագրավորման վարդակից PICkit 2 ծրագրավորողի համար. 6 քայլ

Նկար 16F676 ICSP ծրագրավորման վարդակ PICkit 2 ծրագրավորողի համար. Ես փորձում եմ կառուցել այս երկակի DC շարժիչային մոդուլը իմ ռոբոտային նախագծի համար: Եվ ես տարածք չունեի PCB- ի վրա ICSP կապի վերնագիր տեղադրելու համար: Այսպիսով, ես արագ ծաղրեցի այս դիզայնը