Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:48.

- Վերջին փոփոխված 2025-01-23 14:48.

Այս ուսանելի ծրագրում մենք պատրաստվում ենք նախագծել SPI Bus Master զրոյից VHDL- ում:

Քայլ 1: SPI- ի ակնարկ

- SPI- ը սինխրոն սերիական ավտոբուս է

- Նրա ժողովրդականությունն ու պարզությունը դե ֆակտո չափանիշ դարձրեցին սերիական հաղորդակցության մեջ

- Ամբողջ դուպլեքս ավտոբուս

- Պարզ արձանագրություն և ամենաարագ սերիական ավտոբուսի շարքում

Քայլ 2: Դիզայնի բնութագրերը

Ահա SPI Master- ի բնութագրերը, որոնք մենք նախագծելու ենք.

- Աջակցում է աշխատանքի բոլոր չորս եղանակներին. դինամիկ կարգավորելի

- Ockամացույցը հնարավորություն է տալիս վերահսկել էներգիայի խնայողությունը

- Ստատիկորեն կարգավորելի բառի երկարությունը և արագությունը

- Մեկանգամյա ընդհատում ինչպես փոխանցման, այնպես էլ ընդունման համար

Քայլ 3: Մեկնարկը

Առաջին հերթին, մեր IP- ն պետք է ունենա երկու ինտերֆեյս: Մեկը սերիական ինտերֆեյս է, իսկ մյուսը ՝ զուգահեռ: Սերիական ինտերֆեյսը բաղկացած է SPI- ի փաստացի ստանդարտ ազդանշաններից `MOSI, MISO, SS, SCLK:

MOSI- ն երբեմն կոչվում է SDO, իսկ MISO- ն `երբեմն SDI:

Սերիական ինտերֆեյսը օգտագործվում է արտաքին ծայրամասային սարքերի, այսինքն ՝ SPI ստրուկների հետ հաղորդակցվելու համար:

Hostուգահեռ ինտերֆեյսը օգտագործվում է մեր հաղորդավարի, այսինքն ՝ միկրոկառավարիչի կամ միկրոպրոցեսորի հետ հաղորդակցվելու համար, որն իրականում Վարպետին ասում է, թե ինչ տվյալներ պետք է հաջորդաբար փոխանցել և ստանալ սերիական գծերի միջոցով: այսինքն ՝ բոլոր տվյալների ավտոբուսները պատկանում են զուգահեռ ինտերֆեյսի:

Մենք ունենք գլոբալ ժամացույց, որը վարում է ներքին SPI տրամաբանությունը, ինչպես նաև SCLK- ը, որը մենք ստեղծում ենք ներքին:

Մենք ունենք նաև որոշ ազդանշաններ, ինչպիսիք են գրել միացնելը, ժամացույցը միացնելը: Եվ ընդհատել և կարգավիճակի այլ ազդակներ:

Քանի որ մենք պետք է գործ ունենանք վերահսկողության բարդ պայմանների հետ, ավելի պարզ է նման սերիական հաղորդակցության IP- ների նախագծումը որպես FSM: Մենք նաև նախագծելու ենք SPI վարպետը որպես FSM: FSM- ը կշարժվի մեկ այլ ներքին ժամացույցով, որը երկու անգամ SCLK է: Այդ ներքին ժամացույցը ստեղծվում է գլոբալ ժամացույցի համաժամանակյա հաշվիչների միջոցով:

Բոլոր վերահսկիչ ազդանշանները, որոնք անցնում են ժամացույցի տիրույթները, ունեն սինխրոնիզատորներ `ավելի ապահով կողմում լինելու համար:

Քայլ 4: SPI Master Core և մոդելավորման ալիքների ձևերի RTL տեսք

Դա մերկ RTL ձևավորում է ՝ առանց օգտագործված FPGA IP- ների: Հետևաբար, դա լիովին դյուրակիր կոդ է ցանկացած FPGA- ի համար:

Խորհուրդ ենք տալիս:

LoRa- ի վրա հիմնված գյուղատնտեսության տեսողական մոնիթորինգի համակարգ Iot - Նախագծված դիմումի ձևավորում Firebase- ի և անկյունայինի միջոցով. 10 քայլ

LoRa- ի վրա հիմնված գյուղատնտեսության տեսողական մոնիտորինգի համակարգ Iot | Firebase & Angular- ի միջոցով ճակատային հավելվածի նախագծում. Նախորդ գլխում մենք խոսում ենք այն մասին, թե ինչպես են սենսորները աշխատում loRa մոդուլով ՝ հրակայունի Realtime տվյալների բազան համալրելու համար, և մենք տեսանք շատ բարձր մակարդակի դիագրամ, թե ինչպես է աշխատում մեր ամբողջ նախագիծը: Այս գլխում մենք կխոսենք այն մասին, թե ինչպես կարող ենք

Հիմնական պարամետրերի ավտոմատ վերահսկմամբ ակվարիումի ձևավորում. 4 քայլ (նկարներով)

Ակվարիումի դիզայն հիմնական պարամետրերի ավտոմատացված վերահսկմամբ. Ներածություն Այսօր ծովային ակվարիումի խնամքը հասանելի է յուրաքանչյուր ակվարիումի համար: Ակվարիում ձեռք բերելու խնդիրը դժվար չէ: Բայց բնակիչների լիարժեք կենսապահովման, տեխնիկական խափանումներից պաշտպանվելու, հեշտ և արագ սպասարկում և խնամք

I2C / IIC LCD էկրան - Օգտագործեք SPI LCD I2C LCD էկրանին ՝ օգտագործելով SPI- ից IIC մոդուլը Arduino- ով. 5 քայլ

I2C / IIC LCD էկրան | Օգտագործեք SPI LCD I2C LCD էկրանին ՝ օգտագործելով SPI- ից IIC մոդուլ Arduino- ով. Բարև տղերք, քանի որ սովորական SPI LCD 1602 -ը չափազանց շատ լարեր ունի միացնելու, այնպես որ շատ դժվար է այն միացնել arduino- ին, բայց շուկայում կա մեկ մոդուլ, որը կարող է փոխակերպեք SPI էկրանը IIC էկրանին, այնպես որ դուք պետք է միացնեք ընդամենը 4 լար

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. 5 քայլ

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. Այս ուսանելի ծրագրում մենք պատրաստվում ենք նախագծել պարզ VGA վերահսկիչ RTL- ում: VGA Controller- ը թվային միացում է, որը նախատեսված է VGA էկրաններ վարելու համար: Այն կարդում է Frame Buffer- ից (VGA Memory), որը ներկայացնում է ցուցադրվող շրջանակը և առաջացնում անհրաժեշտություն

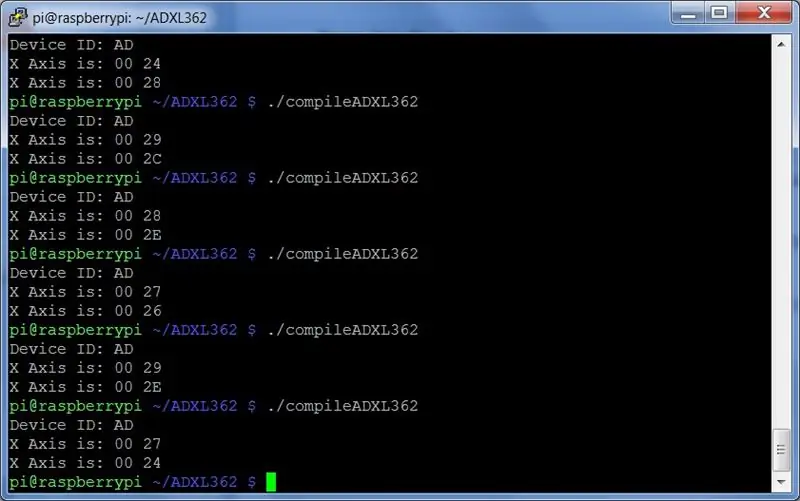

Նախնական* SPI Pi- ի վրա. Հաղորդակցություն SPI 3 առանցքի արագացուցիչի միջոցով `օգտագործելով ազնվամորի Pi: 10 քայլ

Նախնական* SPI Pi- ի վրա. Հաղորդակցություն SPI 3 առանցքի արագացուցիչի միջոցով Raspberry Pi- ի միջոցով. Քայլ առ քայլ ուղեցույց, թե ինչպես կարելի է կարգավորել Raspbian- ը և շփվել SPI սարքի հետ ՝ օգտագործելով bcm2835 SPI գրադարանը (մի փոքր խփված չէ): Սա դեռ շատ նախնական … Ես պետք է ավելացնեմ ֆիզիկական կապի ավելի լավ նկարներ և աշխատեմ որոշ անհարմար կոդերի միջոցով