Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:47.

- Վերջին փոփոխված 2025-01-23 14:48.

Այս նախագծով մեր նպատակն էր ստեղծել մի բան, որը կխնայի համայնքներին էներգիա և ֆինանսական ռեսուրսներ: Շարժման միջոցով ակտիվացված փողոցային լույսերը կանեն այս երկուսն էլ: Ամբողջ երկրում էներգիան վատնում է փողոցների լույսերը լուսավորող դատարկ փողոցները: Մեր փողոցային լուսավորության համակարգը երաշխավորում է, որ լույսերը վառվում են միայն անհրաժեշտության դեպքում ՝ խնայելով անհամար դոլարներ համայնքներից: Շարժման սենսորների միջոցով համակարգը միացնում է լույսերը միայն այն ժամանակ, երբ մեքենաները ներկա են: Նաև հետիոտների անվտանգության համար մենք գործի դրեցինք չեղարկման կոճակ, որը միացնում է փողոցի բոլոր լույսերը: Հետևյալ քայլերը կօգնեն ձեզ հասկանալ, թե ինչպես ենք մենք նախագծել և կառուցել նախագծի մեր փոքրացված մոդելը ՝ օգտագործելով Vivado և Basys 3 տախտակներ:

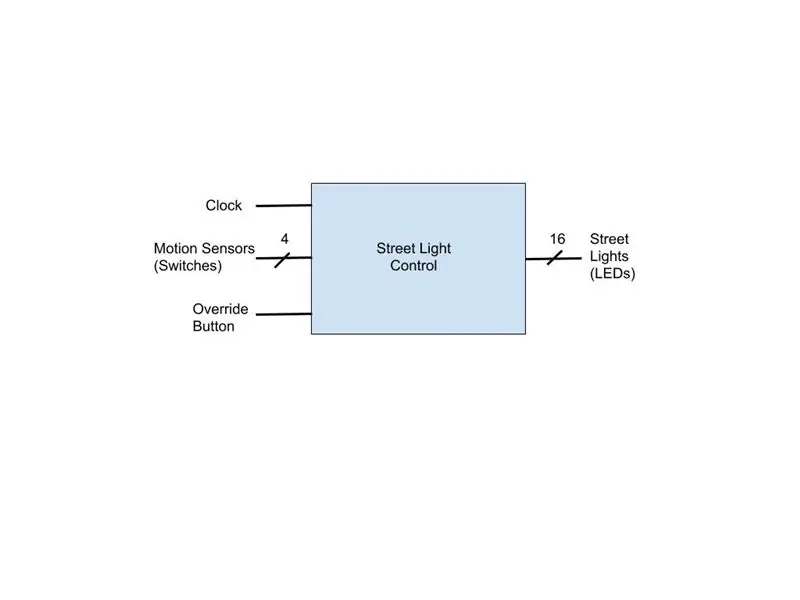

Քայլ 1: System Black Box

Այս նախագիծը սկսեցինք նկարելով սև արկղերի պարզ դիագրամ: Սև արկղի դիագրամը պարզապես ցույց է տալիս այն մուտքերն ու ելքերը, որոնք մեր համակարգը պահանջում է ավարտել բոլոր անհրաժեշտ գործընթացները: Մենք փորձեցինք մեր դիզայնը պահել հնարավորինս պարզ և հիմնական: Համակարգի մեր երեք մուտքերը ներառում էին շարժման տվիչների ավտոբուս (4 -ը ՝ մեր փոքրացված մոդելի համար), հետիոտնների անտեսման կոճակ և ժամացույցի մուտք: Մյուս կողմից, մեր միակ ելքը LED լուսարձակների ավտոբուս է, որը ներկայացնում է մեր փողոցի լույսերը: Այս մոդելի համար մենք 16 փողոցային լուսարձակների սցենար օգտագործեցինք պարզապես այն պատճառով, որ դա Basys 3 տախտակի վրա ներկառուցված LED ելքերի առավելագույն թիվն է: Վերջապես, օգտագործելով այս դիագրամը, մենք կարողացանք ստեղծել մեր Vivado նախագիծը, աղբյուրը և սահմանափակման ֆայլերը `համապատասխան մուտքերով և ելքերով:

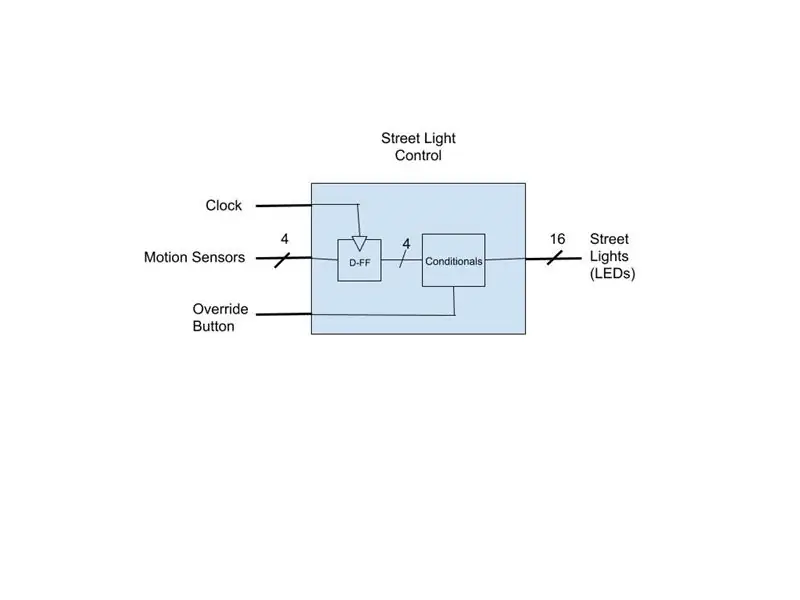

Քայլ 2: Բաղադրիչներ

Այս քայլում մենք ավելի խորն ենք սուզվում ՝ ուսումնասիրելով մեր սև արկղի դիագրամը կազմող բաղադրիչները: Մեր առաջին բաղադրիչը VHDL աղբյուր ֆայլ է, որը պարունակում է D մատնահետքեր: D ֆլիփսոփսերը պարզապես վերցնում են այն ազդանշանը, որը նրանց մուտքագրվում է ժամացույցի աճող եզրին գտնվող սենսորներից և ամրացնում այդ տվյալները մինչև հաջորդ բարձրացող եզրը: Սա թույլ չի տալիս շարժման մեր զգայուն սենսորներին առաջացնել ելքային LED- ների «թարթում»: Բացի այդ, կոճակի մուտքագրման ազդանշանի վրա մենք դնում ենք մեկ D մատով, որպեսզի LED- ները միացված մնան կոճակը սեղմելուց հետո մոտ 5-7 վայրկյան: Մենք նաև սա վազեցինք ժամացույցի բաժանարարի միջով:

clk_div2 սուբյեկտը Port է (clk: std_logic; sclk: out std_logic); վերջ clk_div2;

clk_div2- ի my_clk_div ճարտարապետությունն է

հաստատուն max_count: ամբողջ թիվ: = (300000000); ազդանշան tmp_clk: std_logic: = '0'; սկսել my_div: գործընթացը (clk, tmp_clk) փոփոխական div_cnt: integer: = 0; սկսեք եթե (բարձրանում_եզր (clk)) ապա եթե (div_cnt = MAX_COUNT) ապա tmp_clk <= ոչ tmp_clk; div_cnt: = 0; այլապես div_cnt: = div_cnt + 1; ավարտ, եթե; ավարտ, եթե; sclk <= tmp_clk; ավարտել գործընթացը my_div; վերջ my_clk_div;

Այս դիագրամում մեր վերջին բաղադրիչը վարքային VHDL աղբյուրի ֆայլն է, որը պարունակում է ելքերի պայմանական պայմաններ `ելնելով մուտքային ազդանշանների կազմաձևից:

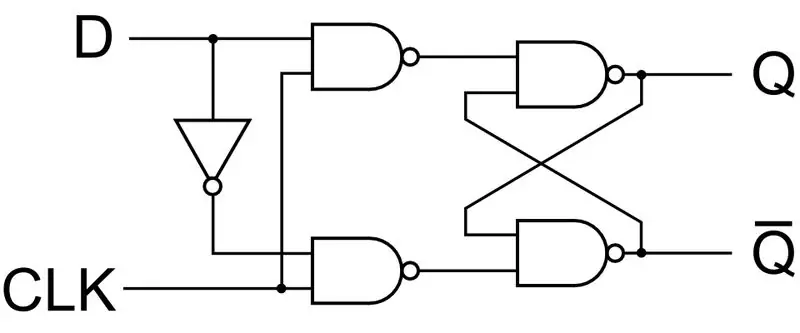

Քայլ 3: D Flip-Flops

Մուտքի ազդանշաններին ամրացված չորս մատնահետքերը էական նշանակություն ունեն մեր համակարգի գործունակության համար: Ինչպես արդեն նշվեց, շարժման զգայուն սենսորներով և անտեսման կոճակով, մատանիները սողնակներն օգտագործում են սողնակներ `միայն ժամացույցի ժամացույցի աճող եզրին մեր մուտքային ազդանշանը թողարկելու համար: Այս հաջորդական տրամաբանությունը նշանակում է, որ մեր փողոցային լույսերը կարող են մի որոշ ժամանակ վառ մնալ արագ շարժումից հետո: D-Flip Flop- ի ծածկագրումը բավականին պարզ է.

beginprocess (CLK) սկսվում է, եթե բարձրանում_եզր (CLK) ապա Q <= D; ավարտ, եթե; ավարտի գործընթացը;

Ամբողջը կարելի է հավաքել մեկ if հայտարարության մեջ: Այս կտորն ունենալուց հետո մենք ստեղծեցինք կառուցվածքային VHDL աղբյուրային ֆայլ, որը պարունակում էր մեր բոլոր չորս անհրաժեշտ մատնահետքերը.

սկսել DFF0: DFF նավահանգստի քարտեզ (CLK => CLK, D => D (0), Q => Q (0)); DFF1: DFF նավահանգստի քարտեզ (CLK => CLK, D => D (1), Q => Q (1)); DFF2: DFF նավահանգստի քարտեզ (CLK => CLK, D => D (2), Q => Q (2)); DFF3: DFF նավահանգստի քարտեզ (CLK => CLK, D => D (3), Q => Q (3));

վերջ Վարքագծային;

Սա օգնում է պահպանել մեր հիմնական կառուցվածքային ֆայլը, որտեղ մենք միավորում ենք համակարգի բոլոր բաղադրիչները շատ ավելի մաքուր և կազմակերպված:

Քայլ 4: Պայմանական պայմաններ

Մեր ծածկագիրը կոմպակտ և արդյունավետ պահելու համար մենք գրեցինք մեր բոլոր պայմանական պայմանները մեկ դեպքի հայտարարության մեջ: Մեր փոքրացված մոդելի համար մենք ունեինք 16 հնարավոր LED ելքային կոնֆիգուրացիա, քանի որ շարժման յուրաքանչյուր ցուցիչ պատասխանատու է 4 LED- ների խմբի համար::

դեպքում NMS- ն այն է, երբ "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED <= "111111111111111111"; վերջնական գործ;

Քայլ 5: Սահմանափակումներ

Vivado- ի միջոցով ձեր մուտքն ու ելքերը ճիշտ ձևակերպելու համար դուք պետք է գործարկեք սահմանափակման ֆայլ, որտեղ նշվում են օգտագործվող բոլոր նավահանգիստները, կոճակները, լուսադիոդները և ժամացույցները:

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports] LED U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACY get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE LED [6]}] set_property IOSTANDARD LVCMOS33 [ստանալ_պորտ {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN V13 8]}] set_property IOSTANDARD LVCMOS33 [ստանալ_պորտեր {LED [8]}] set_property PACKAGE_PIN V3 [ստանալ_պորտեր {LED [9]}] set_property IO STANDARD LVCMOS33 [ստանալ_պորտներ {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [pert] 33 iPad [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD get LVCMOS [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_port] Մարկ B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

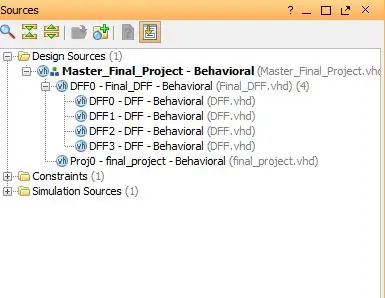

Քայլ 6: Հիմնական աղբյուրի ֆայլ

Այս հիմնական ֆայլում մենք հավաքում ենք նախկինում նշված բոլոր բաղադրիչ աղբյուրների ֆայլերը: Այս ֆայլը գործում է որպես կառուցվածքային կոդ, որը միավորում է տարբեր բաղադրիչները:

սուբյեկտի Master_Final_Project- ը նավահանգիստ է (BTN ՝ STD_LOGIC; CLK ՝ STD_LOGIC; MS ՝ STD_LOGIC_VECTOR (3 իջնում է 0); LED ՝ դուրս STD_LOGIC_VECTOR (15 ներքև 0)); ավարտել Master_Final_Project;

ճարտարապետություն Վարպետի_Վերջնական_նախագծի վարքագիծն է

բաղադրիչ վերջնական նախագիծը նավահանգիստ է (-CLK ՝ STD_LOGIC; NMS ՝ STD_LOGIC_VECTOR (3 իջնում է 0); BTN ՝ STD_LOGIC;-sw. ՝ STD_LOGIC_Vector (1 ներքև 0); LED ՝ դուրս STD_LOGIC_V) վերջնական բաղադրիչ;

բաղադրիչ Final_DFF է

Նավահանգիստ (CLK: STD_LOGIC- ում; D: STD_LOGIC_Vector- ում (3 -ը 0 -ից); Q: STD_LOGIC_Vektor- ից (3 -ից 0 -ից)); վերջնական բաղադրիչ;

ազդանշան DFF02proj30: STD_LOGIC;

ազդանշան DFF12proj74: STD_LOGIC; ազդանշան DFF22proj118: STD_LOGIC; ազդանշան DFF32proj1512: STD_LOGIC;

սկսել

DFF0: Վերջնական_DFF նավահանգստի քարտեզ (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Նախագիծ. Վերջնական_նախագծի նավահանգստի քարտեզ (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); վերջ Վարքագծային;

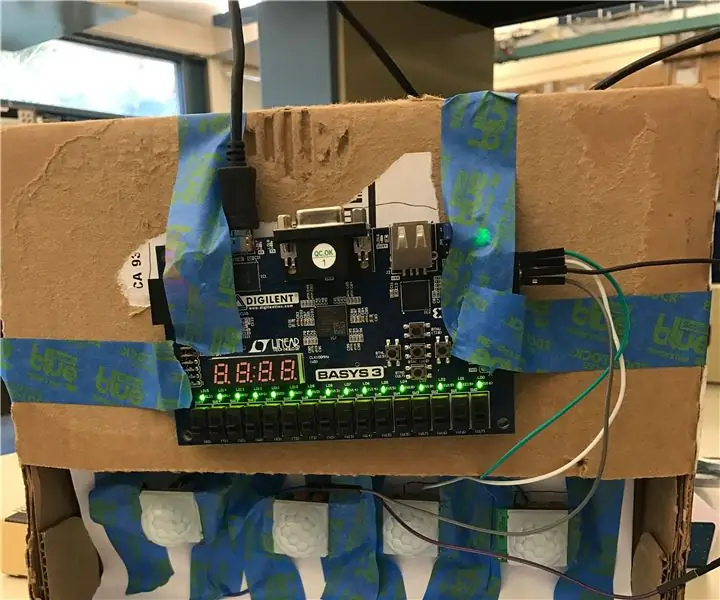

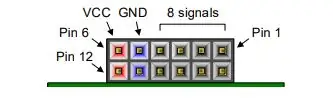

Քայլ 7: Հավաքում

Այս նախագծի ապարատային հավաքումը նվազագույն է: Միակ պահանջվող կտորները հետևյալն են.

1. Basys 3 տախտակ (1)

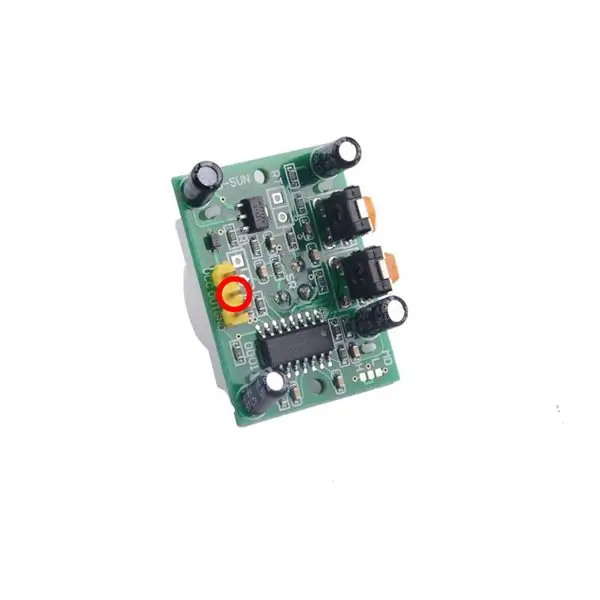

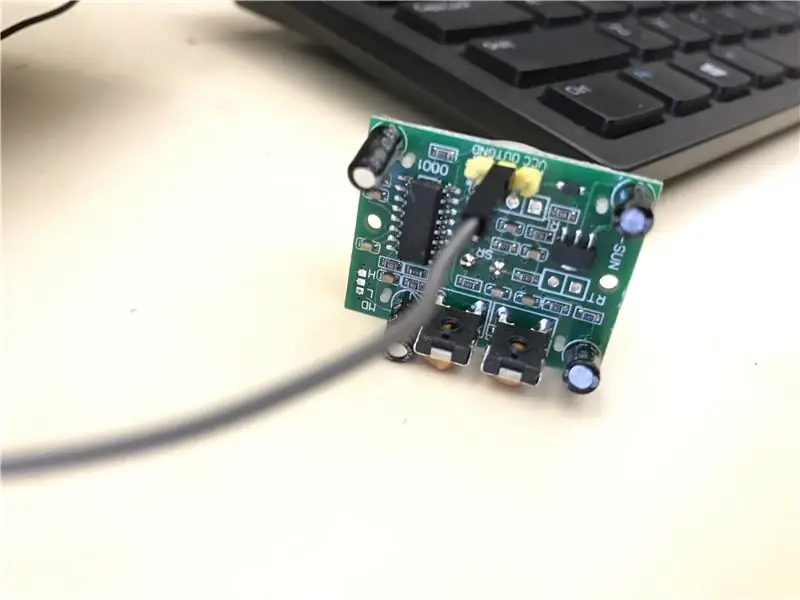

2. Շարժման էժան տվիչներ, որոնք կարելի է գտնել այստեղ Amazon- ում: (4)

3. Արականից իգական սեռի ներկայացուցիչներ (4)

Վեհաժողով:

1. Միացրեք 4 արական հոսանք PMod վերնագրի JB նավահանգիստներին 1-4 (տես նկարը):

2. Միացրեք կանացի ծայրերը շարժման տվիչի յուրաքանչյուր ելքային քորոցին:

Քայլ 8: adingրագիրը բեռնելը

Այժմ մենք պատրաստ ենք բեռնել VHDL հիմնական աղբյուրի ֆայլը Basys 3 տախտակին: Համոզվեք, որ գործարկում եք սինթեզ, իրականացում և ստեղծում բիթստրիմի ստուգում `հնարավոր սխալների համար: Եթե բոլորը հաջողությամբ աշխատեն, բացեք ապարատային կառավարիչը և ծրագրավորեք Basys 3 սարքը: Ձեր նախագիծն այժմ ավարտված է:

Խորհուրդ ենք տալիս:

Շարժման ակտիվացված Cosplay Wings- ը Circuit Playground Express- ի միջոցով - մաս 1: 7 քայլ (նկարներով)

Շարժման ակտիվացված Cosplay Wings- ը Circuit Playground Express- ի միջոցով - մաս 1. Սա երկու մասից բաղկացած նախագծի մի մասն է, որում ես ձեզ ցույց կտամ մի զույգ ավտոմատացված փերի թևեր պատրաստելու իմ ընթացքը: Նախագծի առաջին մասը թևերի մեխանիկա, իսկ երկրորդ մասը դարձնում է այն կրելի, և ավելացնում թևերը

Ուլտրաձայնային տվիչի միջոցով ավտոմատ փողոցային լույսեր `3 քայլ

Ուլտրաձայնային տվիչի միջոցով ավտոմատ փողոցային լույսեր. Երբևէ մտածե՞լ եք, որ ինչպես են փողոցային լույսերը ավտոմատ կերպով միանում գիշերը և ինքնաբերաբար անջատվում առավոտյան: Կա՞ որևէ մարդ, ով միանում/անջատում է այս լույսերը: Փողոցի լույսերը միացնելու մի քանի եղանակ կա, բայց հետևյալ գ

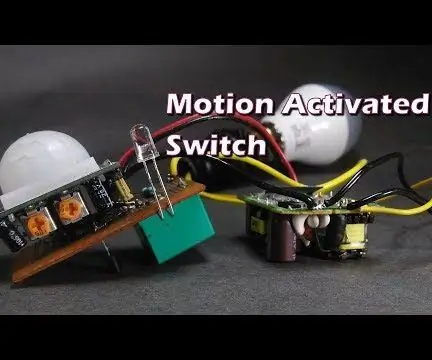

Շարժման ակտիվացված լամպի անջատիչ `3 քայլ

Շարժման ակտիվացված լամպի անջատիչ. Ամեն անգամ, երբ դուրս ենք գալիս գրասեղանից կամ սենյակից, ժամանակի մեծ մասը մոռանում ենք այնտեղ լույսերն անջատել: Սա հանգեցնում է էլեկտրաէներգիայի կորստի և ձեր էլեկտրաէներգիայի հաշիվների ավելացման: Բայց ինչ, եթե լույսերը ինքնաբերաբար անջատվեն, սենյակից դուրս գալուց հետո: Այո

Multi -Channel Sonoff - Ձայնի ակտիվացված լույսեր. 4 քայլ (նկարներով)

Multi-Channel Sonoff-Ձայնի ակտիվացված լույսեր. 5 տարի առաջ իմ խոհանոցի լույսերը գնում էին անելու ճանապարհով: Երթուղու լուսավորությունը ձախողվում էր, իսկ հաշվիչի լուսավորությունը պարզապես աղբ էր: Նաև ցանկանում էի լուսավորությունը բաժանել ալիքների, որպեսզի ավելի լավ լուսավորեմ սենյակը տարբեր

Շարժման դետեկտորի ակտիվացված ունայնության լույս. 6 քայլ

Motion Detector Activated Vanity Light. Ես eBay- ում գնել եմ ինֆրակարմիր շարժման հայտնաբերման միավոր 1.50 դոլարով և որոշել եմ այն լավ օգտագործել: Ես կարող էի պատրաստել իմ սեփական շարժման դետեկտորային տախտակը, բայց 1.50 դոլարով (որը ներառում է զգայունությունը կարգավորելու և ժամանակաչափը անջատելու համար նախատեսված 2 զամբյուղ) դա չէր անի