Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:47.

- Վերջին փոփոխված 2025-01-23 14:48.

Ինձ ծանրաբեռնում են այս բլոգում ստացած արձագանքները: Շնորհակալ եմ տղաներին, որ այցելեցիք իմ բլոգը և ինձ դրդեցիք կիսվել իմ գիտելիքներով ձեզ հետ: Այս անգամ ես կներկայացնեմ մեկ այլ հետաքրքիր մոդուլի դիզայն, որը մենք տեսնում ենք բոլոր SOC- ներում `Interrupt Controller:

Մենք նախագծելու ենք պարզ, բայց հզոր Programրագրավորվող ընդհատումների վերահսկիչ: Դա ամբողջովին կարգավորելի և պարամետրավորված դիզայն է, որը շարժական է հարթակներում: Ես դա նախագծեցի այն բանից հետո, երբ շատ կարդացի որոշ ընդհատումների վերահսկիչ ճարտարապետությունների մասին, ինչպիսիք են NVIC, 8259a, RISC-V PLIC, Microblaze's INTC և այլն: Հուսով եմ, որ այս բլոգը օգտակար կլինի ձեզ համար և կօգնի ձեզ համտեսել, թե ինչպես է ընդհատումները մշակվում պրոցեսորի կողմից: ընդհատումների վերահսկիչի օգնությամբ:

Քայլ 1: Տեխնիկական պայմաններ

Ստորև բերված են IP- ի բնութագրերը.

- AHB3-Lite ինտերֆեյս:

-

Ստատիկապես կարգավորվող պարամետրեր.

- Արտաքին ընդհատումների աղբյուրների քանակը. ապահովում է մինչև 63 ընդհատում:

- Առաջնահերթ մակարդակների համարը; աջակցում է մինչև 63 մակարդակ:

- Բնադրման մակարդակների քանակը; ապահովում է բնադրման մինչև 8 մակարդակ:

- Ավտոբուսի լայնությունը; 32 կամ 64:

- Գլոբալ և տեղական դիմակներով ընդհատումներ:

- Յուրաքանչյուր ընդհատման համար դինամիկ կարգավորելի առաջնահերթության մակարդակ:

- Գործողության երկու եղանակ ՝ Լրիվ ներդիր ռեժիմ և հավասար առաջնահերթություն:

- Աջակցում է ակտիվ բարձր մակարդակի զգայուն ընդհատումներին:

Դիզայնում օգտագործվում է RISC-V PLIC- ի բնութագրերը `ոգեշնչված ձեռքերի սեղմման մեխանիզմը:

Ընդհատման նախապատվությունը ներշնչված է 8259 ա-ից

Այլ ընթերցումներ. Microblaze INTC, NVIC

Քայլ 2. PIC- ի ակնարկ

Mրագրավորվող ընդհատումների վերահսկիչը (PIC) ստանում է բազմաթիվ ընդհատումներ արտաքին ծայրամասերից և դրանք միավորում է մեկ ընդհատման ելքի մեջ `նպատակային պրոցեսորի միջուկին:

PIC- ը վերահսկվում է վերահսկողության և կարգավիճակի գրանցամատյանների միջոցով: Բոլոր PIC գրանցամատյանները հիշողության քարտեզագրված են և հասանելի AHB3-Lite ավտոբուսային միջերեսի միջոցով:

Ռեգիստրային բանկը բաղկացած է կազմաձևման գրանցամատյանից, միացման ռեգիստրներից, առկախ մատյաններից, սպասարկման մատյաններից, առաջնահերթ գրանցիչներից և ID գրանցամատյաններից, որոնք բնորոշ են ընդհատումների վերահսկիչներին:

Կազմաձևման գրանցամատյանը օգտագործվում է PIC- ի աշխատանքի ռեժիմը սահմանելու համար: Այն կարող է աշխատել կամ ամբողջությամբ ներդրված ռեժիմում, կամ հավասար առաջնահերթության ռեժիմում:

Յուրաքանչյուր ընդհատման կարող են տրվել առաջնահերթություններ և անհատապես քողարկվել: Աջակցվում է նաև բոլոր ընդհատումների գլոբալ դիմակավորմանը:

Ռեգիստրային բանկը համագործակցում է Priority Resolver- ի և BTC- ի (Երկուական-ծառ-համեմատող) հետ `լուծումներ առկախող ընդհատումների առաջնահերթությունները լուծելու և համապատասխանաբար հաստատման համար: ID գրանցամատյանը պարունակում է ամենակարևոր առաջնահերթ սպասվող ընդհատման ID- ն:

Քայլ 3. RTL նախագծում և իրականացում

PIC- ի դիզայնը շեշտը դնում է առաջնահերթությունների լուծման ուշացման նվազեցման վրա, որը դիզայնի առավել ժամանակային կարևոր մասն է: Քանի որ դիզայնը լուծում է առաջնահերթությունները մեկ ժամացույցի ցիկլում, կատարումը նվազում է Log2 բարդությամբ աղբյուրների թվի ավելացմամբ:

Դիզայնը հաջողությամբ իրականացվեց, և ժամանակը ստուգվեց մինչև Artix-7 FPGA- ների հետևյալ հաճախականությունները:

- Մինչև 15 աղբյուր ՝ 100 ՄՀց

- Մինչև 63 աղբյուր ՝ 50 ՄՀց

Միայն PIC- ով ավելացված ընդհատման լատենտությունը 3 ժամային ցիկլ է (առանց պրոցեսորի համատեքստի անջատման ժամանակը և առաջին ISR հրահանգի բերման ժամանակը):

Քայլ 4: Կարևոր նշումներ և կից ֆայլեր

Կարևոր նշումներ

- Եթե AHB3-Lite ինտերֆեյսը անցանկալի է, կարող եք փոխել վերին մոդուլը և օգտագործել PIC- ի կմախքի դիզայնը: Այնուամենայնիվ, տրամադրվող թեստային նստարանը IP- ի համար է `AHB3-Lite ինտերֆեյսով:

- PIC IP v1.0- ը լիովին շարժական, մերկ RTL ձևավորում է:

- Ֆունկցիոնալորեն ստուգված է երկու ռեժիմների վրա աշխատելու համար:

Կից ֆայլեր

- Դիզայնի կոդեր և testbench VHDL- ում:

- IP- ի ամբողջական փաստաթղթավորում:

Դա բաց կոդով ձևավորում է … Ազատ զգացեք օգտագործել…

Quանկացած հարցման համար, ցանկացած ժամանակ.

Միտու Ռաջ

Խորհուրդ ենք տալիս:

Ընթացիկ ռեժիմի վրա հիմնված տատանումների նախագծում D դասի ձայնային հզորության ուժեղացուցիչների համար `6 քայլ

Ընթացիկ ռեժիմի վրա հիմնված տատանումների նախագծում D դասի ձայնային հզորության ուժեղացուցիչների համար. Վերջին տարիներին D դասի աուդիո հզորության ուժեղացուցիչները դարձել են նախընտրելի լուծում դյուրակիր աուդիո համակարգերի համար, ինչպիսիք են MP3- ը և բջջային հեռախոսները `բարձր արդյունավետության և էներգիայի ցածր սպառման պատճառով: Տատանողը D au դասի կարևոր մասն է

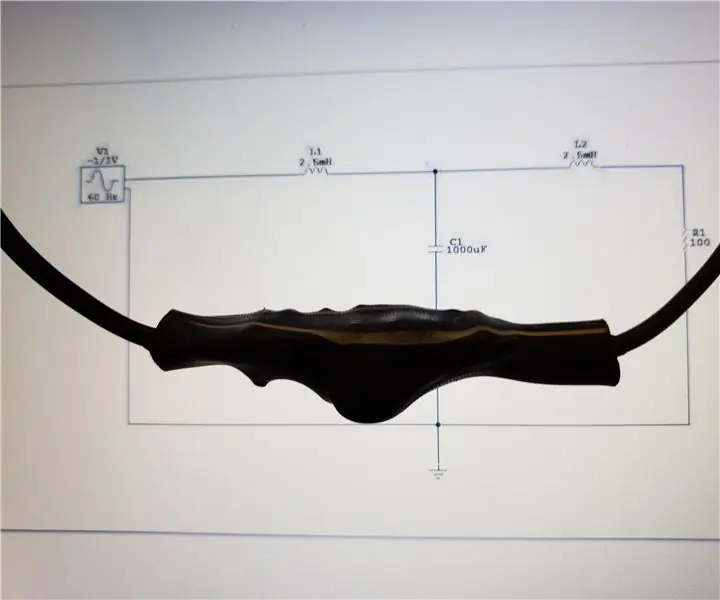

Android հեռախոսի լիցքավորիչի համար Power Line զտիչի նախագծում և կառուցում. 5 քայլ

Android հեռախոսի լիցքավորիչի համար Power Line ֆիլտրի նախագծում և կառուցում. Այս հրահանգում ես ցույց կտամ, թե ինչպես վերցնել ստանդարտ USB մինի USB լարը, այն առանձնացնել մեջտեղում և տեղադրել զտիչի միացում, որը կնվազեցնի ավելորդ աղմուկը կամ հեշը, որն արտադրվում է android- ի տիպիկ սնուցման աղբյուրի միջոցով: Ես ունեմ շարժական մ

VHDL- ում պարզ քառակողմ ասոցիատիվ քեշի վերահսկիչի նախագծում. 4 քայլ

VHDL- ում պարզ քառակողմ ասոցիատիվ քեշի վերահսկիչի ձևավորում. Այս անգամ մենք մի քայլ առաջ ենք գնում: Մենք նախագծելու ենք մի պարզ քառակողմ ասոցիատիվ քեշի վերահսկիչ: Առավելություն? Ավելի քիչ բաց թողնված տոկոսադրույք, բայց կատարման գնով

VHDL- ում պարզ քեշի վերահսկիչի ձևավորում. 4 քայլ

VHDL- ում պարզ քեշի վերահսկիչի ձևավորում. Ես գրում եմ սա ուսանելի, քանի որ մի փոքր դժվար գտա որոշ տեղեկանք VHDL կոդ ստանալ `քեշի վերահսկիչ սովորելու և սկսելու համար: Այսպիսով, ես ինքս զրոյից նախագծեցի քեշի վերահսկիչ և այն հաջողությամբ փորձարկեցի FPGA- ի վրա: Ես ունեմ պ

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. 5 քայլ

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. Այս ուսանելի ծրագրում մենք պատրաստվում ենք նախագծել պարզ VGA վերահսկիչ RTL- ում: VGA Controller- ը թվային միացում է, որը նախատեսված է VGA էկրաններ վարելու համար: Այն կարդում է Frame Buffer- ից (VGA Memory), որը ներկայացնում է ցուցադրվող շրջանակը և առաջացնում անհրաժեշտություն