Բովանդակություն:

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:47.

- Վերջին փոփոխված 2025-01-23 14:48.

Իմ նախորդ հրահանգում մենք տեսանք, թե ինչպես նախագծել պարզ ուղղակի քարտեզագրված քեշի վերահսկիչ: Այս անգամ մենք մի քայլ առաջ ենք գնում: Մենք նախագծելու ենք մի պարզ քառակողմ ասոցիատիվ քեշի վերահսկիչ: Առավելություն? Ավելի քիչ բաց թողնված տոկոսադրույք, բայց կատարման գնով: Ինչպես և իմ նախորդ բլոգը, մենք նախագծում և ընդօրինակում էինք մի ամբողջ պրոցեսոր, հիմնական հիշողություն և քեշ միջավայր `մեր քեշի վերահսկիչը փորձարկելու համար: Հուսով եմ, որ տղերք դա օգտակար տեղեկանք եք համարում հասկացությունները հասկանալու և ապագայում ձեր սեփական քեշի վերահսկիչները նախագծելու համար: Քանի որ պրոցեսորի (փորձնական նստարանի) մոդելը և հիմնական հիշողության համակարգը նույնն են, ինչ իմ նախորդ բլոգը, ես դրանք այլևս չեմ բացատրի: Խնդրում ենք անդրադառնալ նախորդ հրահանգին `դրա վերաբերյալ մանրամասների համար:

Քայլ 1: Տեխնիկական պայմաններ

Արագ հայացք այստեղ ներկայացված Cache Controller- ի բնութագրերի միջոցով.

- Քառուղի Set Associative Cache Controller (անցեք այս հղումով, եթե փնտրում եք Direct Mapped Cache Controller):

- Մեկ բանկային, արգելափակող քեշ:

- Գրելու հիթեր գրելու քաղաքականություն:

- Գրելու բացթողումներ գրելու շուրջ-քաղաքականություն:

- Reeառերի կեղծ-LRU (pLRU) փոխարինման քաղաքականություն:

- Պիտակների զանգվածը վերահսկիչի ներսում:

- Կարգավորելի պարամետրեր:

Cache Memory- ի և Main Memory- ի կանխադրված բնութագրերը նույնն են, ինչ իմ նախորդ հրահանգի դեպքում: Խնդրում ենք անդրադառնալ նրանց:

Քայլ 2: Ամբողջ համակարգի RTL տեսք

Վերևի մոդուլի ամբողջական RTL ներկայացումը ներկայացված է Նկարում (առանց պրոցեսորի): Ավտոբուսների կանխադրված բնութագրերն են.

- Բոլոր տվյալների ավտոբուսները 32-բիթանոց ավտոբուսներ են:

- Հասցեի ավտոբուս = 32-բիթանոց ավտոբուս (Բայց Հիշողության միջոցով այստեղ հասցեագրելի է ընդամենը 10 բիթ):

- Տվյալների արգելափակում = 128 բիթ (կարդալու համար լայն թողունակության ավտոբուս):

- Բոլոր բաղադրիչները շարժվում են նույն ժամացույցով:

Քայլ 3: Թեստի արդյունքներ

Վերևի մոդուլը փորձարկվել է Test Bench- ի միջոցով, որը պարզապես մոդելավորում է ոչ խողովակաշարային պրոցեսոր, ինչպես դա արեցինք վերջին հրահանգում: Թեստային նստարանը հաճախակի ստեղծում է Հիշողության համար կարդալու/գրելու տվյալների պահանջներ: Սա ծաղրում է տիպիկ «Բեռնում» և «Պահել» հրահանգները, որոնք տարածված են պրոցեսորի կողմից կատարված բոլոր ծրագրերում:

Թեստի արդյունքները հաջողությամբ ստուգեցին Cache Controller- ի ֆունկցիոնալությունը: Ստորև բերված են թեստերի վիճակագրությունը.

- Բոլոր կարդալ/գրել Miss և Hit ազդանշանները ճիշտ են ստեղծվել:

- Տվյալների կարդալու/գրելու բոլոր գործողությունները հաջող էին բոլոր չորս եղանակներով:

- pLRU ալգորիթմը հաջողությամբ հաստատված է քեշի տողերի փոխարինման համար:

- Տվյալների անհամապատասխանության/անհամապատասխանության խնդիրներ չեն հայտնաբերվել:

- Դիզայնը հաջողությամբ հաստատվեց Maxm- ի համար: Clամացույցի հաճախականությունը = 100 ՄՀց Xilinx Virtex-4 ML-403 տախտակում (ամբողջ համակարգ), 110 ՄՀց միայն Cache Controller- ի համար:

- Արգելափակված RAM- ները եզրակացվեցին հիմնական հիշողության համար: Մնացած բոլոր զանգվածները կիրառվել են LUT- երի վրա:

Քայլ 4: Կից ֆայլեր

Հետևյալ ֆայլերը կցված են այստեղ այս բլոգին.

- . VHD ֆայլեր Cache Controller, Cache Data Array, Main Memory System:

- Փորձնական նստարան:

- Փաստաթղթեր Cache Controller- ի վերաբերյալ:

Նշումներ

- Անցեք փաստաթղթերը ՝ այստեղ ներկայացված Cache Controller- ի բնութագրերը լիովին հասկանալու համար:

- Կոդի ցանկացած փոփոխություն կախված է այլ մոդուլներից: Այսպիսով, փոփոխությունները պետք է արվեն խելամիտ:

- Ուշադրություն դարձրեք իմ տված բոլոր մեկնաբանություններին և վերնագրերին:

- Եթե ինչ -ինչ պատճառներով, հիմնական հիշողության համար արգելափակված RAM- ները չեն եզրակացվում, Նվազեցրեք հիշողության չափը, որին հաջորդում են հասցեների ավտոբուսի լայնությունների փոփոխությունները ֆայլերում և այլն: Որպեսզի նույն հիշողությունը կարող է իրականացվել կամ LUT- ներով կամ Distributed RAM- ով: Սա կփրկի երթուղու ժամանակը և ռեսուրսները: Կամ, գնացեք FPGA- ի հատուկ փաստաթղթերը և գտեք Block RAM- ի համար համատեղելի կոդը և համապատասխանաբար խմբագրեք ծածկագիրը, և օգտագործեք նույն հասցեի ավտոբուսի լայնության բնութագրերը: Նույն տեխնիկան Altera FPGA- ների համար:

Խորհուրդ ենք տալիս:

Ընթացիկ ռեժիմի վրա հիմնված տատանումների նախագծում D դասի ձայնային հզորության ուժեղացուցիչների համար `6 քայլ

Ընթացիկ ռեժիմի վրա հիմնված տատանումների նախագծում D դասի ձայնային հզորության ուժեղացուցիչների համար. Վերջին տարիներին D դասի աուդիո հզորության ուժեղացուցիչները դարձել են նախընտրելի լուծում դյուրակիր աուդիո համակարգերի համար, ինչպիսիք են MP3- ը և բջջային հեռախոսները `բարձր արդյունավետության և էներգիայի ցածր սպառման պատճառով: Տատանողը D au դասի կարևոր մասն է

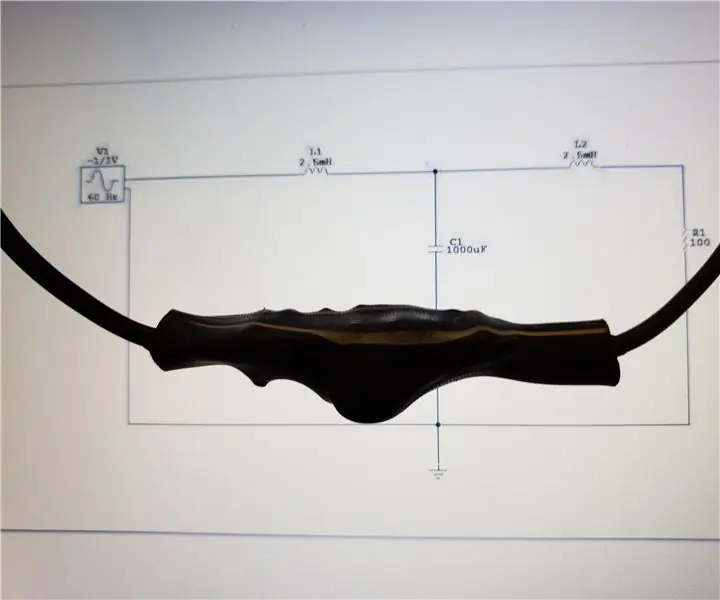

Android հեռախոսի լիցքավորիչի համար Power Line զտիչի նախագծում և կառուցում. 5 քայլ

Android հեռախոսի լիցքավորիչի համար Power Line ֆիլտրի նախագծում և կառուցում. Այս հրահանգում ես ցույց կտամ, թե ինչպես վերցնել ստանդարտ USB մինի USB լարը, այն առանձնացնել մեջտեղում և տեղադրել զտիչի միացում, որը կնվազեցնի ավելորդ աղմուկը կամ հեշը, որն արտադրվում է android- ի տիպիկ սնուցման աղբյուրի միջոցով: Ես ունեմ շարժական մ

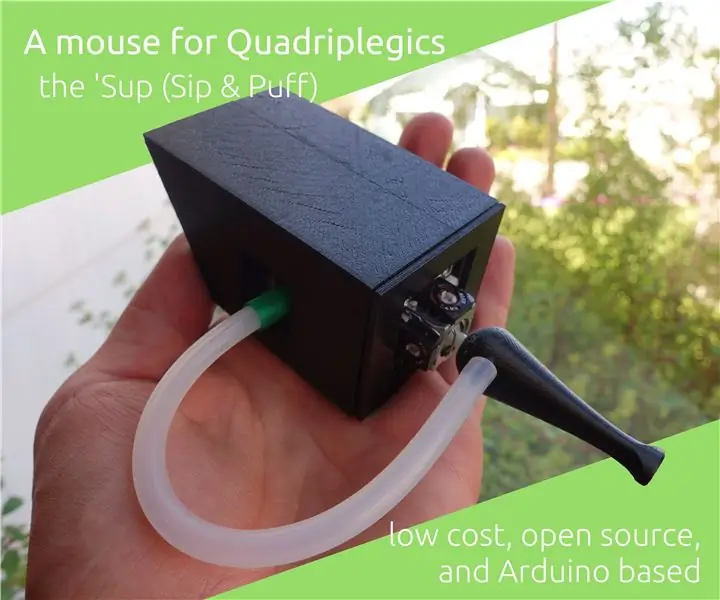

The 'Sup - մուկ `քառակողմ ունեցող մարդկանց համար` ցածր գնով և բաց կոդով. 12 քայլ (նկարներով)

«Sup - մուկ ՝ քառատիկ բարդությամբ տառապող մարդկանց համար. Նրանք ունեն մի ընկեր ՝ Ալենին, ով քառակողմ տառապում է լեռնային հեծանվով վթարի հետևանքով: Ես և Ֆելիքսը (իմ ընկերը) արագ հետազոտություններ կատարեցինք

VHDL ծրագրավորվող ընդհատումների վերահսկիչի նախագծում. 4 քայլ

VHDL- ում ծրագրավորվող ընդհատումների վերահսկիչի ձևավորում. Շնորհակալ եմ տղաներին, որ այցելեցիք իմ բլոգը և ինձ դրդեցիք կիսվել իմ գիտելիքներով ձեզ հետ: Այս անգամ, ես կներկայացնեմ մեկ այլ հետաքրքիր մոդուլի դիզայն, որը մենք տեսնում ենք բոլոր SOC- ներում `Interrupt C

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. 5 քայլ

VHDL- ի և Verilog- ի պարզ VGA վերահսկիչի ձևավորում. Այս ուսանելի ծրագրում մենք պատրաստվում ենք նախագծել պարզ VGA վերահսկիչ RTL- ում: VGA Controller- ը թվային միացում է, որը նախատեսված է VGA էկրաններ վարելու համար: Այն կարդում է Frame Buffer- ից (VGA Memory), որը ներկայացնում է ցուցադրվող շրջանակը և առաջացնում անհրաժեշտություն