Բովանդակություն:

- Քայլ 1. Ի՞նչ է Vivado HLS- ը:

- Քայլ 2: HLS տեսադարան

- Քայլ 3: Սինթեզավորում

- Քայլ 4. Տարբերակ և արտահանման այլ տեղեկություններ

- Քայլ 5. Արտահանում դեպի Vivado IP գրադարան

- Քայլ 6. Սինթեզ և արտահանման վերլուծություն

- Քայլ 7: IP գրադարանի ավելացում Vivado- ում

- Քայլ 8: Կատարելագործում

- Քայլ 9: Լրացուցիչ մանրամասներ և տեղեկատվություն

- Քայլ 10: Ելք և մուտքագրում

- Քայլ 11: AXI Գրանցեք միջերես

- Քայլ 12: Dataflow Pragma

- Հեղինակ John Day day@howwhatproduce.com.

- Public 2024-01-30 09:51.

- Վերջին փոփոխված 2025-01-23 14:48.

Երբևէ ցանկացե՞լ եք իրական ժամանակում տեսանյութերի մշակում ՝ առանց մեծ ուշացում ավելացնելու կամ ներկառուցված համակարգում: Երբեմն դա անելու համար օգտագործվում են FPGA (դաշտային ծրագրավորվող դարպասների զանգվածներ); սակայն, տեսամշակման ալգորիթմներ գրել ապարատային բնութագրերի լեզուներով, ինչպիսիք են VHDL- ը կամ Verilog- ը լավագույն դեպքում հիասթափեցնող է: Մուտքագրեք Vivado HLS- ը ՝ Xilinx գործիքը, որը թույլ է տալիս ծրագրավորել C ++ միջավայրում և դրանից սարքավորել սարքավորման ճշգրտման լեզվի ծածկագիր:

Պահանջվող ծրագրակազմ.

- Vivado HLS

- Վիվադո

- (Եթե օգտագործում եք AXI գրանցամատյանները) Vivado SDK

(Լրացուցիչ) Ներբեռնեք Xilinx- ի պատրաստված օրինակները այստեղ.

Xilinx HLS տեսանյութերի օրինակներ

Քայլ 1. Ի՞նչ է Vivado HLS- ը:

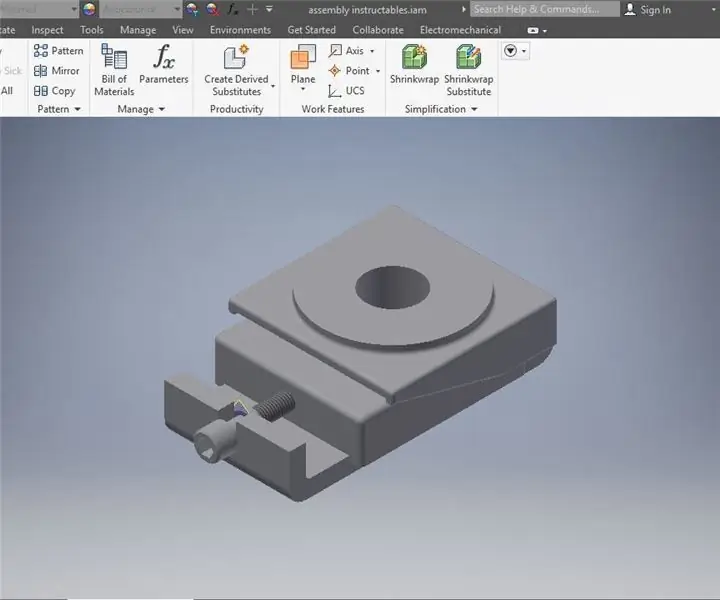

Vivado HLS- ը գործիք է, որն օգտագործվում է c ++ - ի ծածկագիրը վերածելու ապարատային կառուցվածքների, որոնք կարող են իրականացվել FPGA- ի վրա: Այն ներառում է այս զարգացումը կատարելու IDE- ն: Երբ ավարտեք HLS- ի ծածկագրի մշակումը, կարող եք արտահանել ձեր գեներացված IP- ն ձևաչափով Vivado- ի հետ օգտագործելու համար:

Ներբեռնեք կցված ֆայլերը և տեղադրեք դրանք մոտակայքում, որտեղ ստեղծելու եք ձեր նախագիծը: (դրանք վերանվանել «top.cpp» և «top.h», եթե նրանք ունեն պատահական անուն)

Քայլ 2: HLS տեսադարան

HLS տեսադարանն այս փաստաթղթում ունի հղումային նախագծերով փաստաթղթեր ՝ XAPP1167 Մեկ այլ լավ ռեսուրս է դրա մասին Xilinx Wiki էջը:

Սկսեք Vivado HLS- ը:

Ստեղծեք նոր նախագիծ:

Վերցրեք նախորդ քայլին ներբեռնված ֆայլերը և դրանք ավելացրեք որպես սկզբնական ֆայլեր: (Նշում. Ֆայլերը չեն պատճենվում նախագծում, այլ մնում են այնտեղ, որտեղ կան)

Այնուհետեւ օգտագործեք «Թերթել» կոճակը `վերին գործառույթը ընտրելու համար:

Հաջորդ էջում ընտրեք Xilinx հատվածը, որն օգտագործում եք:

Քայլ 3: Սինթեզավորում

Լուծում => Գործարկել C սինթեզ => Ակտիվ լուծում

7 227.218 վայրկյանից հետո դա պետք է արվի: (Նշում. Ձեր սինթեզի իրական ժամանակը կտատանվի `կախված բազմաթիվ գործոններից)

Քայլ 4. Տարբերակ և արտահանման այլ տեղեկություններ

Տարբերակի համարները փոխազդում են Vivado- ի հետ ՝ պատճառ դառնալով, որ դուք կարողանաք IP- ն թարմացնել դիզայնի մեջ: Եթե դա աննշան տարբերակի փոփոխություն է, այն կարող է կատարվել տեղում, մինչ հիմնական տարբերակի փոփոխությունները պահանջում են, որ դուք ձեռքով ավելացնեք նոր բլոկը և հեռացնեք հինը: Եթե ձեր միջերեսները չեն փոխվել, և տարբերակի թարմացումն աննշան է, թարմացումը կարող է լինել կատարվում է ամբողջությամբ ինքնաբերաբար ՝ սեղմելով թարմացման IP կոճակը: Դուք կարող եք գործարկել «report_ip_status» - ը Vivado tcl վահանակում ՝ ձեր IP- ի կարգավիճակը տեսնելու համար:

Տեղադրեք տարբերակի համարները և այլ տեղեկություններ Solution => Solution Settings…

Այլապես, այս կարգավորումները կարող են սահմանվել արտահանման ընթացքում:

Քայլ 5. Արտահանում դեպի Vivado IP գրադարան

Լուծում => Արտահանել RTL

Եթե նախորդ քայլին IP գրադարանի տվյալները չեք սահմանել, կարող եք դա անել հիմա:

Քայլ 6. Սինթեզ և արտահանման վերլուծություն

Այս էկրանին մենք կարող ենք տեսնել մեր արտահանվող մոդուլի վիճակագրությունը, որը ցույց է տալիս, որ այն համապատասխանում է մեր ժամացույցի տևողությանը ՝ 10ns (100 ՄՀց) և յուրաքանչյուր ռեսուրսից որքան է օգտագործում:

Այս, մեր սինթեզային հաշվետվության և Տվյալների հոսքի վերլուծության համադրությամբ մենք կարող ենք տեսնել, որ այն տևում է 317338 ժամացույցի ցիկլեր * 10 նց ժամային ժամանակաշրջան * 14 խողովակաշարային փուլ = 0.04442732 վայրկյան: Նշանակում է, որ մեր պատկերի մշակման արդյունքում ավելացված ընդհանուր ուշացումը վայրկյանի մեկ քսաներորդից պակաս է (երբ նշվում է նպատակային 100 ՄՀց հաճախականությամբ):

Քայլ 7: IP գրադարանի ավելացում Vivado- ում

Ձեր սինթեզված IP բլոկն օգտագործելու համար հարկավոր է այն ավելացնել Vivado- ին:

Vivado- ում ձեր նախագծին ավելացրեք IP պահոց ՝ գնալով IP կատալոգ և աջ սեղմելով ընտրելով «Ավելացնել պահեստ…»

Գնացեք դեպի ձեր Vivado HLS ծրագրի գրացուցակը և ընտրեք լուծումների գրացուցակը:

Այն պետք է զեկուցի իր գտած IP- ին:

Քայլ 8: Կատարելագործում

Երբեմն դուք պետք է փոփոխություններ կատարեք ձեր HLS բլոկում Vivado դիզայնի մեջ ներառելուց հետո:

Դա անելու համար կարող եք կատարել փոփոխություններ և վերաինտինեզավորել և արտահանել IP- ն ավելի բարձր տարբերակի համարով (տե՛ս նախորդ քայլի մանրամասները ՝ հիմնական կամ փոքր տարբերակի համարի փոփոխությունների վերաբերյալ):

Նոր տարբերակի արտահանումը փոխելուց հետո թարմացրեք ձեր IP պահոցները Vivado- ում: Դա կարելի է անել, երբ Vivado- ն նկատում է, որ IP- ն փոխվել է պահեստում, կամ ձեռքով ակտիվացվել: (Ուշադրություն դարձրեք, եթե սկզբից հետո թարմացնեք ձեր IP պահոցները, բայց մինչև արտահանումը HLS- ում ավարտվի, IP- ն ժամանակավորապես այնտեղ չի լինի, սպասեք, որ այն ավարտվի և նորից թարմացվի):

Այս պահին պետք է հայտնվի պատուհան այն տեղեկատվությամբ, որ IP- ն փոխվել է սկավառակի վրա և հնարավորություն է տալիս այն թարմացնել «Upgrade Selected» կոճակով: Եթե փոփոխությունը փոքր տարբերակի փոփոխություն էր, և միջերեսներից ոչ մեկը չէր փոխվել, ապա այդ կոճակը սեղմելը ինքնաբերաբար հին IP- ն կփոխարինի նորով, այլապես կարող է ավելի շատ աշխատանք պահանջվել:

Քայլ 9: Լրացուցիչ մանրամասներ և տեղեկատվություն

Հետևյալ քայլերը ավելի շատ տեղեկություններ են տալիս այն մասին, թե ինչպես է աշխատում HLS սինթեզը և ինչ կարող եք անել դրա հետ:

HLS սինթեզված IP բլոկ օգտագործող նախագծի համար տե՛ս այս հրահանգը:

Քայլ 10: Ելք և մուտքագրում

Վերջնական IP բլոկի ելքերն ու մուտքերը որոշվում են վերին գործառույթից տվյալների հոսքի սինթեզատոր վերլուծությունից:

VHDL- ի կամ verilog- ի նման, HLS- ն թույլ է տալիս մանրամասներ նշել IP- ի միջև կապերի մասին: Այս տողերը դրա օրինակներն են.

անվավեր պատկերի_ֆիլտր (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE առանցքի նավահանգիստ = վիդեո_փաթեթում = INPUT_STREAM #pragma HLS INTERFACE առանցքի նավահանգիստ = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUSS = BACH = 0

Դուք կարող եք տեսնել, թե ինչպես են IP հրահանգի վրա ցուցադրվող նավահանգիստներն ազդում այդ հրահանգների վրա:

Քայլ 11: AXI Գրանցեք միջերես

Ձեր IP բլոկից դեպի PS մուտքագրում/ելք ստանալու համար դա անելու լավ միջոց է AXI ինտերֆեյսը:

Դուք կարող եք դա նշել ձեր HLS ծածկագրում, ներառյալ այն օֆսեթները, որոնք կօգտագործվեն հետագայում տվյալ արժեքին մուտք գործելու համար.

անվավեր պատկերի_ֆիլտր (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite նավահանգիստ = x փաթեթ = CONTROL_BUS օֆսեթ = 0x14

#pragma HLS INTERFACE s_axilite նավահանգիստ = y փաթեթ = CONTROL_BUS օֆսեթ = 0x1C #pragma HLS տվյալների հոսք

x = 42;

y = 0xDEADBEEF; }

Vivado- ում պատշաճ կերպով միանալուց հետո կարող եք մուտք գործել արժեքներ ՝ օգտագործելով այս կոդը Vivado SDK- ում.

#ներառել «պարամետրերը.հ»

#սահմանել xregoff 0x14 #սահմանել yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Սա ձեզ կստանա 42 -ով x- ով և 0xdeadbeef- ով `y- ով

Քայլ 12: Dataflow Pragma

#Պրագմայի ՏՎՅԱԼՆԵՐԻ ներսում կոդի ներդրման եղանակը փոխվում է սովորական C ++ - ից: Կոդը հաղորդվում է այնպես, որ բոլոր հրահանգներն անընդհատ գործարկվեն տվյալների տարբեր մասերում (մտածեք դա, ինչպես գործարանի հավաքման գիծը, յուրաքանչյուր կայան անընդհատ աշխատում է մեկ գործառույթ կատարելով և փոխանցելով այն հաջորդ կայանին)

պատկերից կարող եք տեսնել, որ հրահանգներից յուրաքանչյուրը

Չնայած սովորական փոփոխականներ թվալուն, img օբյեկտները իրականում իրականացվում են որպես փոքր բուֆեր ՝ հրամանների միջև: Պատկերը որպես ֆունկցիայի մուտքագրում օգտագործելը «սպառում» է այն և այն այլևս պիտանի չի դարձնում: (Հետեւաբար կրկնօրինակ հրամանների անհրաժեշտությունը)

Խորհուրդ ենք տալիս:

Համագումարի հաջողում ՝ հարթեցման բլոկի համար. 30 քայլ

Համագումարի հաջողություն հարթեցման բլոկի համար. Սա բժիշկ Դուգլաս Լեկորչիկի վերջին տեխնիկական գրառումն է Berea College TAD 330 դասարանում, որը լրացվում է Կարմադրի Սանտյագոյի կողմից, 28 ապրիլի, 2020 թ

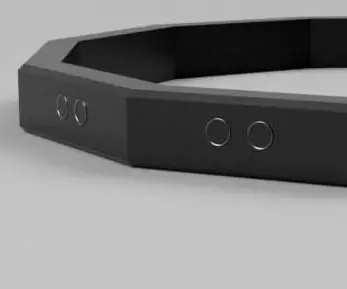

Phono -Chronoxyle - 360 աստիճանի սինթեզ ՝ 3 քայլ (նկարներով)

Phono -Chronoxyle - 360 Degree Synth. Julien Signolet քանդակագործ, որը բնակվում է Փարիզից և երաժիշտ Մաթիաս Դուրանդը, մոտեցան ինձ Փարիզի Parc Floral- ում Nuit Blanche 2019 ինտերակտիվ ձայնային տեղադրման համար: Տեղադրումը դռնփակ կլիներ, և ես ներկա չէի լինի մեջ

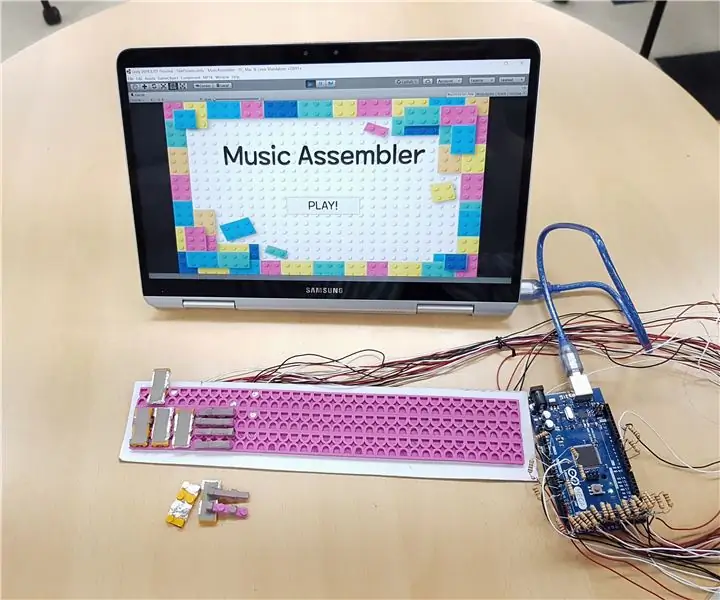

Երաժշտական հավաքող. Ինտեգրված վիրտուալ երաժշտական գործիք ՝ բլոկի տեսքով հպման տվիչով ՝ 4 քայլ

Երաժշտական հավաքող. Ինտեգրված վիրտուալ երաժշտական գործիք ՝ բլոկի տեսքով հպման տվիչով. Կան շատ մարդիկ, ովքեր ցանկանում են սովորել երաժշտական գործիք նվագել: Lyավոք, նրանցից ոմանք դա չեն սկսում գործիքների բարձր գնի պատճառով: Դրա հիման վրա մենք որոշեցինք կատարել վիրտուալ երաժշտական գործիքների համակարգ ՝ նվազեցնելու սկսնակ բյուջեն

Retro խոսքի սինթեզ: Մաս ՝ 12 IoT, տան ավտոմատացում ՝ 12 քայլ (նկարներով)

Retro խոսքի սինթեզ: Մաս ՝ 12 IoT, տնային ավտոմատացում. Այս հոդվածը 12 -րդն է տնային ավտոմատացման վերաբերյալ ցուցումների շարքում, որոնք փաստում են, թե ինչպես կարելի է ստեղծել և ինտեգրել IoT Retro խոսքի սինթեզի սարք գոյություն ունեցող տան ավտոմատացման համակարգում, ներառյալ բոլոր անհրաժեշտ ծրագրային գործառույթները, որոնք հնարավորություն են տալիս

Ձեր համակարգչի ձայնի անալոգային սինթեզ. 10 քայլ (նկարներով)

Ձեր համակարգչում անալոգային ձայնի սինթեզ. Հավանում եք այդ հին անալոգային սինթեզատորների ձայնը: Wantանկանում եք խաղալ մեկի հետ ձեր սեփական ժամանակին, ձեր սեփական վայրում, այնքան ժամանակ, որքան ցանկանում եք, անվճար: Այստեղ է, որ իրականանում են Մոգի ձեր ամենավայրի երազանքները: Դուք կարող եք դառնալ էլեկտրոնային ձայնագրման արտիստ կամ արդար